## Concept Block Library LL984 Volume 3

840 USE 506 00 eng Version 2.6

© 2002 Schneider Electric All Rights Reserved

## **Table of Contents**

|           | About the book XI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | The chapters marked gray are not included in this volume.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Part I    | General Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 1 | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 2 | Instruction Groups         5           At a Glance         5           Instruction Groups         6           ASCII Functions         7           Counters and Timers Instructions         7           Fast I/O Instructions         8           Loadable DX         9           Math Instructions         9           Matrix Instructions         11           Miscellaneous         12           Move Instructions         13           Skips/Specials         13           Special Instructions         14           Coils, Contacts and Interconnects         14 |

| Chapter 3 | Closed Loop Control / Analog Values       15         At a Glance       15         Closed Loop Control / Analog Values       16         PCFL Subfunctions       17         A PID Example       21         PID2 Level Control Example       25                                                                                                                                                                                                                                                                                                                         |

| Chapter 4  | Formatting Messages for ASCII READ/WRIT Operations 29 At a Glance                                                                                                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5  | Interrupt Handling                                                                                                                                               |

| Chapter 6  | Subroutine Handling39Subroutine Handling39                                                                                                                       |

| Chapter 7  | Installation of DX Loadables                                                                                                                                     |

| Chapter 8  | Coils, Contacts and Interconnects       43         At a Glance       43         Coils       44         Contacts       46         Interconnects (Shorts)       48 |

| Part II    | Instruction Descriptions                                                                                                                                         |

| Chapter 9  | AD16: Ad 16 Bit       55         At a Glance       55         Short Description       56         Representation       56                                         |

| Chapter 10 | ADD: Addition 57                                                                                                                                                 |

| Chapter 11 | AND: Logical And59                                                                                                                                               |

| Chapter 12 | BCD: Binary to Binary Code                                                                                                                                       |

| Chapter 13 | BLKM: Block Move                                                                                                                                                 |

| Chapter 14 | BLKT: Block to Table69                                                                                                                                           |

| Chapter 15 | BMDI: Block Move with Interrupts Disabled                                                                                                                        |

| Chapter 16 | BROT: Bit Rotate                                                                                                                                                 |

| Chapter 17 | CHS: Configure Hot Standby 79                                                                                                                                    |

| Chapter 18 | CKSM: Check Sum                                                                                                                                                  |

| Chapter 19 | CMPR: Compare Register                                                                                                                                           |

| Chapter 20 | COMP: Complement a Matrix93                                        |

|------------|--------------------------------------------------------------------|

| Chapter 21 | DCTR: Down Counter97                                               |

| Chapter 22 | DIOH: Distributed I/O Health99                                     |

| Chapter 23 | DIV: Divide103                                                     |

| Chapter 24 | DLOG: Data Logging for PCMCIA Read/Write Support107                |

| Chapter 25 | DRUM: DRUM Sequencer113                                            |

| Chapter 26 | DV16: Divide 16 Bit117                                             |

| Chapter 27 | EMTH: Extended Math                                                |

| Chapter 28 | EMTH-ADDDP: Double Precision Addition127                           |

| Chapter 29 | EMTH-ADDFP: Floating Point Addition                                |

| Chapter 30 | EMTH-ADDIF: Integer + Floating Point Addition                      |

| Chapter 31 | EMTH-ANLOG: Base 10 Antilogarithm                                  |

| Chapter 32 | EMTH-ARCOS: Floating Point Arc Cosine of an Angle (in Radians)     |

| Chapter 33 | EMTH-ARSIN: Floating Point Arcsine of an Angle (in Radians)147     |

| Chapter 34 | EMTH-ARTAN: Floating Point Arc Tangent of an Angle (in Radians)151 |

| Chapter 35 | EMTH-CHSIN: Changing the Sign of a Floating Point Number           |

| Chapter 36 | EMTH-CMPFP: Floating Point Comparison                              |

| Chapter 37 | EMTH-CMPIF: Integer-Floating Point Comparison163                   |

| Chapter 38 | EMTH-CNVDR: Floating Point Conversion of Degrees to Radians        |

| Chapter 39 | EMTH-CNVFI: Floating Point to Integer Conversion                   |

| Chapter 40 | EMTH-CNVIF: Integer-to-Floating Point Conversion175                |

| Chapter 41 | EMTH-CNVRD: Floating Point Conversion of Radians to Degrees        |

| Chapter 42 | EMTH-COS: Floating Point Cosine of an Angle (in Radians)      |

|------------|---------------------------------------------------------------|

| Chapter 43 | EMTH-DIVDP: Double Precision Division 187                     |

| Chapter 44 | EMTH-DIVFI: Floating Point Divided by Integer 191             |

| Chapter 45 | EMTH-DIVFP: Floating Point Division                           |

| Chapter 46 | EMTH-DIVIF: Integer Divided by Floating Point 199             |

| Chapter 47 | EMTH-ERLOG: Floating Point Error Report Log 203               |

| Chapter 48 | EMTH-EXP: Floating Point Exponential Function 207             |

| Chapter 49 | EMTH-LNFP: Floating Point Natural Logarithm 211               |

| Chapter 50 | EMTH-LOG: Base 10 Logarithm                                   |

| Chapter 51 | EMTH-LOGFP: Floating Point Common Logarithm 219               |

| Chapter 52 | EMTH-MULDP: Double Precision Multiplication                   |

| Chapter 53 | EMTH-MULFP: Floating Point Multiplication                     |

| Chapter 54 | EMTH-MULIF: Integer x Floating Point Multiplication 231       |

| Chapter 55 | EMTH-PI: Load the Floating Point Value of "Pi" 235            |

| Chapter 56 | EMTH-POW: Raising a Floating Point Number to an Integer Power |

| Chapter 57 | EMTH-SINE: Floating Point Sine of an Angle (in Radians) . 243 |

| Chapter 58 | EMTH-SQRFP: Floating Point Square Root247                     |

| Chapter 59 | EMTH-SQRT: Floating Point Square Root                         |

| Chapter 60 | EMTH-SQRTP: Process Square Root                               |

| Chapter 61 | EMTH-SUBDP: Double Precision Subtraction 259                  |

| Chapter 62 | EMTH-SUBFI: Floating Point - Integer Subtraction 263          |

| Chapter 63 | EMTH-SUBFP: Floating Point Subtraction                        |

| Chapter 64 | EMTH-SUBIF: Integer - Floating Point Subtraction 271          |

| Chapter 65 | EMTH-TAN: Floating Point Tangent of an Angle (in Radians)     |

| Chapter 66 | ESI: Support of the ESI Module279            |

|------------|----------------------------------------------|

| Chapter 67 | EUCA: Engineering Unit Conversion and Alarms |

| Chapter 68 | FIN: First In                                |

| Chapter 69 | FOUT: First Out313                           |

| Chapter 70 | FTOI: Floating Point to Integer317           |

| Chapter 71 | HLTH: History and Status Matrices319         |

| Chapter 72 | IBKR: Indirect Block Read                    |

| Chapter 73 | IBKW: Indirect Block Write                   |

| Chapter 74 | ICMP: Input Compare                          |

| Chapter 75 | ID: Interrupt Disable                        |

| Chapter 76 | IE: Interrupt Enable347                      |

| Chapter 77 | IMIO: Immediate I/O351                       |

| Chapter 78 | IMOD: Interrupt Module Instruction357        |

| Chapter 79 | ITMR: Interrupt Timer                        |

| Chapter 80 | ITOF: Integer to Floating Point371           |

| Chapter 81 | JSR: Jump to Subroutine373                   |

| Chapter 82 | LAB: Label for a Subroutine375               |

| Chapter 83 | LOAD: Load Flash379                          |

| Chapter 84 | MAP 3: MAP Transaction                       |

| Chapter 85 | MBIT: Modify Bit                             |

| Chapter 86 | MBUS: MBUS Transaction395                    |

| Chapter 87 | MRTM: Multi-Register Transfer Module405      |

| Chapter 88 | MSTR: Master                                 |

| Chapter 89 | MU16: Multiply 16 Bit                        |

| Chapter 90 | MUL: Multiply455                             |

| Chapter 91 | NBIT: Bit Control457                         |

| Chapter 92  | NCBT: Normally Closed Bit459                                   |

|-------------|----------------------------------------------------------------|

| Chapter 93  | NOBT: Normally Open Bit                                        |

| Chapter 94  | NOL: Network Option Module for Lonworks 463                    |

| Chapter 95  | OR: Logical OR                                                 |

| Chapter 96  | PCFL: Process Control Function Library 471                     |

| Chapter 97  | PCFL-AIN: Analog Input                                         |

| Chapter 98  | PCFL-ALARM: Central Alarm Handler 485                          |

| Chapter 99  | PCFL-AOUT: Analog Output                                       |

| Chapter 100 | PCFL-AVER: Average Weighted Inputs Calculate 493               |

| Chapter 101 | PCFL-CALC: Calculated preset formula 499                       |

| Chapter 102 | PCFL-DELAY: Time Delay Queue 503                               |

| Chapter 103 | PCFL-EQN: Formatted Equation Calculator 509                    |

| Chapter 104 | PCFL-INTEG: Integrate Input at Specified Interval 515          |

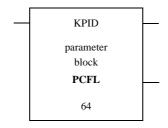

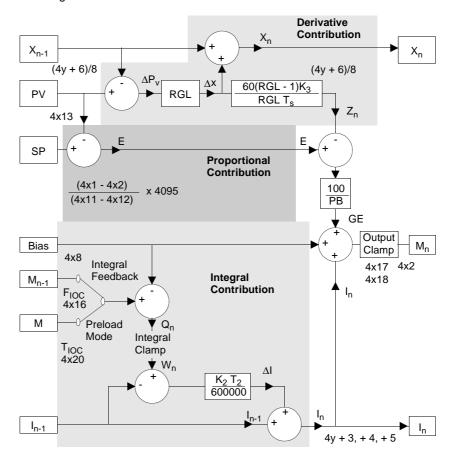

| Chapter 105 | PCFL-KPID: Comprehensive ISA Non Interacting PID 519           |

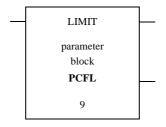

| Chapter 106 | PCFL-LIMIT: Limiter for the Pv                                 |

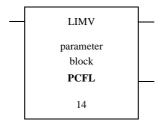

| Chapter 107 | PCFL-LIMV: Velocity Limiter for Changes in the Pv 529          |

| Chapter 108 | PCFL-LKUP: Look-up Table                                       |

| Chapter 109 | PCFL-LLAG: First-order Lead/Lag Filter 537                     |

| Chapter 110 | PCFL-MODE: Put Input in Auto or Manual Mode 541                |

| Chapter 111 | PCFL-ONOFF: ON/OFF Values for Deadband 545                     |

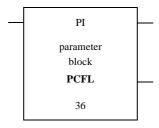

| Chapter 112 | PCFL-PI: ISA Non Interacting PI                                |

| Chapter 113 | PCFL-PID: PID Algorithms 555                                   |

| Chapter 114 | PCFL-RAMP: Ramp to Set Point at a Constant Rate 561            |

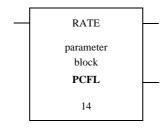

| Chapter 115 | PCFL-RATE: Derivative Rate Calculation over a Specified Timeme |

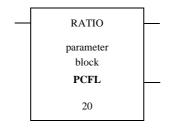

| Chapter 116 | PCFL-RATIO: Four Station Ratio Controller 571                  |

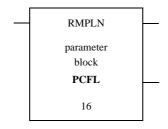

| Chapter 117 | PCFL-RMPLN: Logarithmic Ramp to Set Point 577                  |

|             |                                                                |

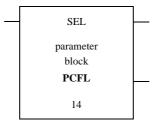

| Chapter 118 | PCFL-SEL: Input Selection581              |

|-------------|-------------------------------------------|

| -           |                                           |

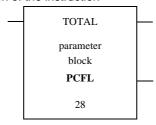

| Chapter 119 | PCFL-TOTAL: Totalizer for Metering Flow   |

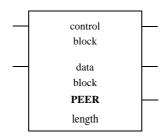

| Chapter 120 | PEER: PEER Transaction591                 |

| Chapter 121 | PID2: Proportional Integral Derivative595 |

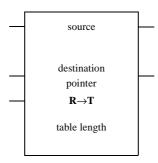

| Chapter 122 | R —> T: Register to Table                 |

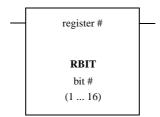

| Chapter 123 | RBIT: Reset Bit613                        |

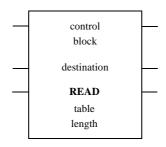

| Chapter 124 | READ: Read615                             |

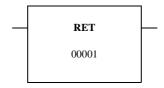

| Chapter 125 | RET: Return from a Subroutine621          |

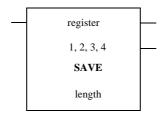

| Chapter 126 | SAVE: Save Flash                          |

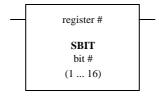

| Chapter 127 | SBIT: Set Bit627                          |

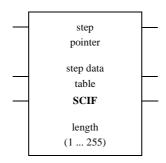

| Chapter 128 | SCIF: Sequential Control Interfaces       |

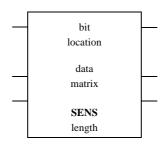

| Chapter 129 | SENS: Sense                               |

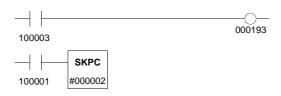

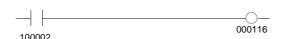

| Chapter 130 | SKPC: Skip (Constants)                    |

| Chapter 131 | SKPR: Skip (Registers)                    |

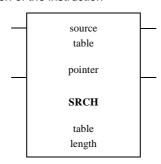

| Chapter 132 | SRCH: Search                              |

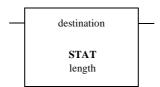

| Chapter 133 | STAT: Status                              |

| Chapter 134 | SU16: Subtract 16 Bit                     |

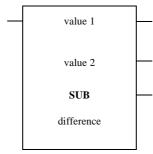

| Chapter 135 | SUB: Subtraction677                       |

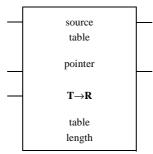

| Chapter 136 | T>R: Table to Register                    |

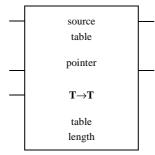

| Chapter 137 | T>T: Table to Table                       |

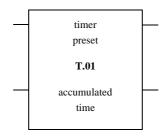

| Chapter 138 | T.01 Timer: One Hundredth Second Timer687 |

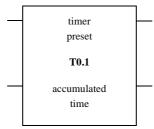

| Chapter 139 | T0.1 Timer: One Tenth Second Timer689     |

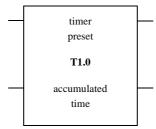

| Chapter 140 | T1.0 Timer: One Second Timer              |

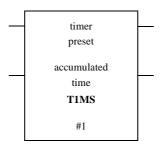

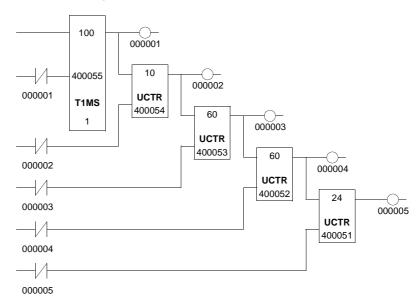

| Chapter 141 | T1MS Timer: One Millisecond Timer693      |

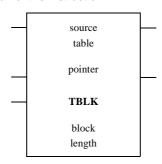

| Chapter 142 | TBLK: Table to Block                      |

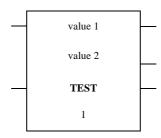

| Chapter 143 | TEST: Test of 2 Values                    |

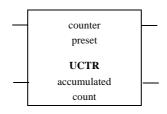

| Chapter 144 | UCTR: Up Counter                  |

|-------------|-----------------------------------|

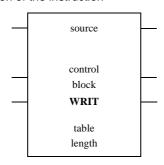

| Chapter 145 | WRIT: Write707                    |

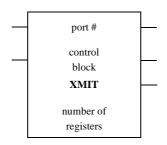

| Chapter 146 | XMIT: XMIT Communication Block713 |

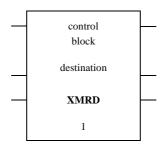

| Chapter 147 | XMRD: Extended Memory Read        |

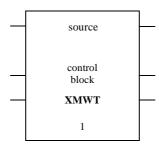

| Chapter 148 | XMWT: Extended Memory Write727    |

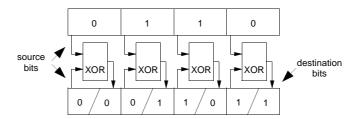

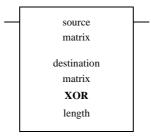

| Chapter 149 | XOR: Exclusive OR                 |

| Glossary    | 735                               |

| Index       |                                   |

### About the book

### At a Glance

**Document Scope**

This documentation will help you configure the LL984-instructions from Concept.

**Validity Note**

This documentation is valid for Concept 2.6 under Microsoft Windows 98, Microsoft Windows 2000, Microsoft Windows XP and Microsoft Windows NT 4.x.

**Note:** For additional up-to-date notes, please refer to the file README of Concept.

## Related Documents

| Title of Documentation                                       | Reference Number |

|--------------------------------------------------------------|------------------|

| Concept Installation Instruction                             | 840 USE 502 00   |

| Concept User Manual                                          | 840 USE 503 00   |

| Concept IEC Library                                          | 840 USE 504 00   |

| Concept-EFB User Manual                                      | 840 USE 505 00   |

| XMIT Function Block User Guide                               | 840 USE 113 00   |

| Network Option Module for LonWorks                           | 840 USE 109 00   |

| Quantum Hot Standby Planning and Installation Guide          | 840 USE 106 00   |

| Modbus Plus Network Planning and Installation Guide          | 890 USE 100 00   |

| Quantum 140 ESI 062 10 ASCII Interface Module User Guide     | 840 USE 1116 00  |

| Modicon S980 MAP 3.0 Network Interface Controller User Guide | GM-MAP3-001      |

### **User Comments**

We welcome your comments about this document. You can reach us by e-mail at  $\mathsf{TECHCOMM}@\mathsf{modicon.com}$

# **PCFL: Process Control Function Library**

96

### At a Glance

### Introduction

This chapter describes the instruction PCFL.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 472  |

| Representation        | 473  |

| Parameter Description | 474  |

### **Short Description**

# Function Description

The PCFL instruction gives you access to a library of process control functions utilizing analog values.

PCFL operations fall into three major categories:

- Advanced Calculations

- Signal Processing

- Regulatory Control

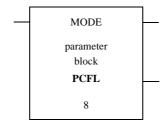

A PCFL function is selected from a list of alphabetical subfunctions in a pulldown menu in the panel software, and the subfunction is displayed in the top node of the instruction (see the table *Function (Top Node)*, *p. 474* for a list of subfunctions and descriptions).

PCFL uses the same FP library as EMTH. If the PLC that you are using for PCFL does not have the onboard 80x87 math coprocessor chip, calculations take a comparatively long time to execute. PLCs with the math coprocessor can solve PCFL calculations ten times faster than PLCs without the chip. Speed, however, should not be an issue for most traditional process control applications where solution times are measured in seconds, not milliseconds.

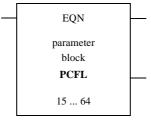

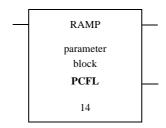

## Representation

## Symbol

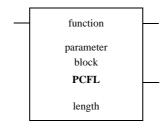

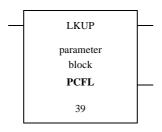

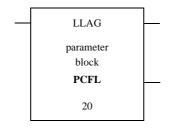

### Representation of the instruction

# Parameter Description

### Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type          | Meaning                                                                                                        |

|-------------------------------------|------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None               | ON = enables specified process control function                                                                |

| function<br>(top node)              |                        |                    | Selection of process control function (subfunction)                                                            |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT,<br>WORD | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| length (bottom node)                |                        | INT, UINT          | Length of parameter block (depending on selected subfunction                                                   |

| Top output                          | 0x                     | None               | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None               | ON = error                                                                                                     |

## **Parameter Description**

### Function (Top Node)

A subfunction for the selected PCFL library function is specified in the top node:

| Operation             | Subfunction | Description                                                                     | Time-<br>dependent<br>Operations |

|-----------------------|-------------|---------------------------------------------------------------------------------|----------------------------------|

| Advanced              | AVER        | Average weighted inputs                                                         | no                               |

| Calculations          | CALC        | Calculate preset formula                                                        | no                               |

|                       | EQN         | Formatted equation calculator                                                   | no                               |

| Signal                | ALARM       | Central alarm handler for a PV input                                            | no                               |

| Processing            | AIN         | Convert inputs to scaled engineering units                                      | no                               |

|                       | AOUT        | Convert outputs to values in the 0 4095 range                                   | no                               |

|                       | DELAY       | Time delay queue                                                                | yes                              |

|                       | LKUP        | Look-up table                                                                   | no                               |

|                       | INTEG       | Integrate input at specified interval                                           | yes                              |

|                       | LLAG        | First-order lead/lag filter                                                     | yes                              |

|                       | LIMIT       | Limiter for the PV (low/low, low, high, high/high)                              | no                               |

|                       | LIMV        | Velocity limiter for changes in the PV (low, high)                              | yes                              |

|                       | MODE        | Put input in auto or manual mode                                                | no                               |

|                       | RAMP        | Ramp to set point at a constant rate                                            | yes                              |

|                       | RMPLN       | Logarithmic ramp to set point (~2/3 closer to set point for each time constant) | yes                              |

|                       | RATE        | Derivative rate calculation over a specified time                               | yes                              |

|                       | SEL         | High/low/average input selection                                                | no                               |

| Regulatory<br>Control | KPID        | Comprehensive ISA non-interacting proportional-integral-derivative (PID)        | yes                              |

|                       | ONOFF       | Specifies ON/OFF values for deadband                                            | no                               |

|                       | PID         | PID algorithms                                                                  | yes                              |

|                       | PI          | ISA non-interacting PI (with halt/manual/auto operation features)               | yes                              |

|                       | RATIO       | Four-station ratio controller                                                   | no                               |

|                       | TOTAL       | Totalizer for metering flow                                                     | yes                              |

## Advanced Calculations

Advanced calculations are used for general mathematical purposes and are not limited to process control applications. With advanced calculations, you can create custom signal processing algorithms, derive states of the controlled process, derive statistical measures of the process, etc.

Simple math routines have already been offered in the EMTH instruction. The calculation capability included in PCFL is a textual equation calculator for writing custom equations instead of programming a series of math operations one by one.

## Signal Processing

Signal processing functions are used to manipulate process and derived process signals. They can do this in a variety of ways; they linearize, filter, delay, and otherwise modify a signal. This category would include functions such as an Analog Input/Output, Limiters, Lead/Lag, and Ramp generators.

#### Regulatory Control

Regulatory functions perform closed loop control in a variety of applications. Typically, this is a PID (proportional integral derivative) negative feedback control loop. The PID functions in PCFL offer varying degrees of functionality. Function 75, PID, has the same general functionality as the PID2 instruction but uses floating point math and represents some options differently. PID is beneficial in cases where PID2 is not suitable because of numerical concerns such as round-off.

Further information you will find in the section Closed Loop Control (See *PCFL Subfunctions*, p. 17).

## Parameter Block (Middle Node)

The 4x register entered in the middle node is the first in a block of contiguous holding register where the parameters for the specified PCFL operation are stored.

The ways that the various PCFL operations implement the parameter block are described in the description of the various subfunctions (PCFL operations).

Within the parameter block of each PCFL function are two registers used for input and output status.

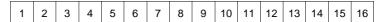

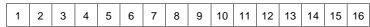

### **Output Flags**

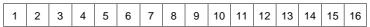

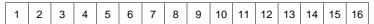

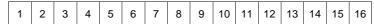

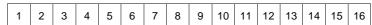

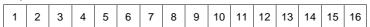

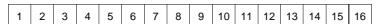

In all PCFL functions, bits 12  $\dots$  16 of the output status register define the following standard output flags:

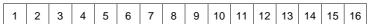

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|-------------------------------------|--|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

|-------------------------------------|--|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Bit         | Function                                                 |  |  |

|-------------|----------------------------------------------------------|--|--|

| 1 - 11      | Not used                                                 |  |  |

| 12          | 1 = Math error - invalid floating point or output        |  |  |

| 13          | 1 = Unknown PCFL function                                |  |  |

| 14 not used |                                                          |  |  |

| 15          | 1 = Size of the allocated register table is too small    |  |  |

| 16          | 1 = Error has occurred - pass power to the bottom output |  |  |

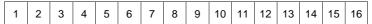

For time-dependent PCFL functions, bits 9 and 11 are also used as follows:

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 1 |  | 4 5 6 | 4 5 6 7 8 9 10 | I   12   13   14   15 |

|------------------------------------|--|-------|----------------|-----------------------|

|------------------------------------|--|-------|----------------|-----------------------|

| Bit   | Function                                                 |  |

|-------|----------------------------------------------------------|--|

| 1 - 8 | Not used                                                 |  |

| 9     | 1 = Initialization working                               |  |

| 10    | Not used                                                 |  |

| 11    | 1 = Illegal solution interval                            |  |

| 12    | 1 = Math error - invalid floating point or output        |  |

| 13    | 1 = Unknown PCFL function                                |  |

| 14    | not used                                                 |  |

| 15    | 1 = Size of the allocated register table is too small    |  |

| 16    | 1 = Error has occurred - pass power to the bottom output |  |

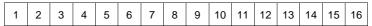

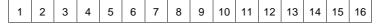

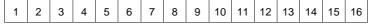

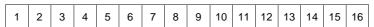

### **Input Flags**

In all PCFL functions, bits 1 and 3 of the input status register define the following standard input flags:

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

|-------------------------------------|

|-------------------------------------|

| Bit                                                                                  | Function           |  |

|--------------------------------------------------------------------------------------|--------------------|--|

| 1 1 = Function initialization complete or in progress<br>0 = Initialize the function |                    |  |

| 2                                                                                    | not used           |  |

| 3                                                                                    | 1 = Timer override |  |

| 4 -16                                                                                | not used           |  |

# Length (Bottom Node)

The integer value entered in the bottom node specifies the length, i.e. the number of registers, of the PCFL parameter block. The maximum allowable length will vary depending on the function you specify.

## **PCFL-AIN: Analog Input**

97

### At a Glance

### Introduction

This chapter describes the subfunction PCFL-AIN.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 480  |

| Representation        | 480  |

| Parameter Description | 481  |

### **Short Description**

## Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Signal Processing*, *p. 475*.

The AIN function scales the raw input produced by analog input modules to engineering values that can be used in the subsequent calculations.

Three scaling options are available:

- Auto input scaling

- Manual input scaling

- Implementing process square root on the input to linearize the signal before scaling

### Representation

### **Symbol**

Representation of the instruction

# Parameter Description

Description of the instruction's parameters

| Parameters                       | State RAM<br>Reference | Data<br>Type | Meaning                                                                                                        |

|----------------------------------|------------------------|--------------|----------------------------------------------------------------------------------------------------------------|

| Top input                        | 0x, 1x                 | None         | ON = enables specified process control function                                                                |

| AIN (top node)                   |                        |              | Selection of the subfunction AIN                                                                               |

| parameter block<br>(middle node) | 4x                     | INT,<br>UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 14 (bottom node)                 |                        | INT,<br>UINT | Length of parameter block for subfunction AIN (can not be changed)                                             |

| Top output                       | 0x                     | None         | ON = operation successful                                                                                      |

| Bottom output                    | 0x                     | None         | ON = error                                                                                                     |

## **Parameter Description**

### Mode of Functioning

AIN supports the range resolutions for following device types: **Quantum Engineering Ranges**

| Resolution | Range: Valid  | Range: Under | Range: Over |

|------------|---------------|--------------|-------------|

| 10 V       | 768 64 768    | 767          | 64 769      |

| V          | 16 768 48 768 | 16 767       | 48 769      |

| 0 10 V     | 0 64 000      | 0            | 64 001      |

| 0 5 V      | 0 32 000      | 0            | 32 001      |

| 1 5 V      | 6 400 32 000  | 6 399        | 32 001      |

### **Quantum Thermocouple**

| Resolution     | Range: Valid   |

|----------------|----------------|

| TC degrees     | -454 +3 308    |

| TC 0.1 degrees | -4 540 +32 767 |

| TC Raw Units   | 0 65 535       |

### **Quantum Voltmeter**

| Resolution | Range: Valid    | Range: Under | Range: Over |

|------------|-----------------|--------------|-------------|

| 10 V       | -10 000 +10 000 | -10 001      | +10 001     |

| 5 V        | -5 000 +5 000   | -5 001       | +5 001      |

| 0 10 V     | 0 10 000        | 0            | 10 001      |

| 0 5 V      | 0 5 000         | 0            | 5 001       |

| 1 5 V      | 1 000 5 000     | 999          | 5 001       |

# Parameter Block (Middle Node)

### The length of the AIN parameter block is 14 registers:

| Register                  | Content                      |

|---------------------------|------------------------------|

| Displayed                 | Input from a 3x register     |

| First implied             | Reserved                     |

| Second implied            | Output Status, p. 482        |

| Third implied             | Input Status, p. 483         |

| Fourth and fifth implied  | Scale 100% engineering units |

| Sixth and seventh implied | Scale 0% engineering units   |

| Eighth and ninth implied  | Manual input                 |

| 10th and 11th implied     | Auto input                   |

| 12th and 13th implied     | Output                       |

### **Output Status**

### Output Status

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14  | 15 | 16 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|-----|----|----|

|   | _ | 0 |   |   | 0 | ' | 0 | 0 | 10 |    | 12 | 10 | 1-7 | 10 | 10 |

| Bit                                                           | Function                                                           |  |  |  |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| 15                                                            | Not used                                                           |  |  |  |  |  |

| 6                                                             | 1 = with TC PSQRT, invalid: in extrapolation range, PSQRT not used |  |  |  |  |  |

| 7                                                             | 1 = input out of range                                             |  |  |  |  |  |

| 8                                                             | 1 = echo under range from input module                             |  |  |  |  |  |

| 9                                                             | 1 = echo over range from input module                              |  |  |  |  |  |

| 10                                                            | 1 = invalid output mode selected                                   |  |  |  |  |  |

| 11                                                            | 1 = invalid Engineering Units                                      |  |  |  |  |  |

| 12 16 Standard output bits (flags) (See Output Flags, p. 476) |                                                                    |  |  |  |  |  |

### **Input Status**

### Input Status

| Bit   | Function                                                                                  |

|-------|-------------------------------------------------------------------------------------------|

| 1 3   | Standard input bits (flags) (See Input Flags, p. 476)                                     |

| 4 8   | Ranges (see following tables)                                                             |

| 9     | 1 = process square root on raw input                                                      |

| 10    | 1 = manual scaling mode<br>0 = auto scaling mode                                          |

| 11    | 1 = extrapolate over-/under-range for auto mode 0 = clamp over-/under-range for auto mode |

| 12 16 | Not used                                                                                  |

## **Quantum Engineering Ranges**

| Bit |   |   |   |   |         |

|-----|---|---|---|---|---------|

| 4   | 5 | 6 | 7 | 8 | Range   |

| 0   | 1 | 0 | 0 | 0 | +/- 10V |

| 0   | 1 | 0 | 0 | 1 | +/- 5V  |

| 0   | 1 | 0 | 1 | 0 | 0 10 V  |

| 0   | 1 | 0 | 1 | 1 | 0 5 V   |

| 0   | 1 | 1 | 0 | 0 | 1 5 V   |

## **Quantum Thermocouple**

| Bit |   |   |   |   |                |

|-----|---|---|---|---|----------------|

| 4   | 5 | 6 | 7 | 8 | Range          |

| 0   | 1 | 1 | 0 | 1 | TC degrees     |

| 0   | 1 | 1 | 1 | 0 | TC 0.1 degrees |

| 0   | 1 | 1 | 1 | 1 | TC raw units   |

### **Quantum Voltmeter**

| Bit |   |   |   |   |         |

|-----|---|---|---|---|---------|

| 4   | 5 | 6 | 7 | 8 | Range   |

| 1   | 0 | 0 | 0 | 0 | +/- 10V |

| 1   | 0 | 0 | 1 | 0 | +/- 5V  |

| 1   | 0 | 1 | 0 | 0 | 0 10 V  |

| 1   | 0 | 1 | 1 | 0 | 0 5 V   |

| 1   | 1 | 0 | 0 | 0 | 1 5 V   |

Note: Bit 4 in this register is nonstandard use.

484 USE 506 00 October 2002

# **PCFL-ALARM: Central Alarm** Handler

98

### At a Glance

### Introduction

This chapter describes the subfunction PCFL-Alarm.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 486  |

| Representation        | 486  |

| Parameter Description | 487  |

### **Short Description**

# Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Signal Processing*, *p. 475*.

The ALARM function gives you a central block for alarm handling where you can set high (H), low (L), high high (HH), and low low (LL) limits on a process variable. ALARM lets you specify

- A choice of normal or deviation operating mode

- Whether to use H/L or both H/L and HH/LL limits

- Whether or not to use deadband (DB) around the limits

### Representation

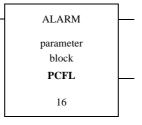

### **Symbol**

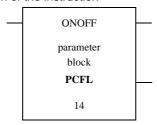

Representation of the instruction

### Parameter Description

Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type          | Meaning                                                                                                        |

|-------------------------------------|------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None               | ON = enables specified process control function                                                                |

| ALARM<br>(top node)                 |                        |                    | Selection of the subfunction ALARM                                                                             |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT,<br>WORD | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 16<br>(bottom node)                 |                        | INT, UINT          | Length of parameter block for subfunction ALARM (can not be changed)                                           |

| Top output                          | 0x                     | None               | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None               | ON = error                                                                                                     |

### **Parameter Description**

### Mode of Functioning

The following operating modes are available:

| Mode                        | Meaning                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal Operating Mode       | ALARM operates directly on the input. Normal is the default condition                                                                                                                                                                                                             |

| Deviation Operating<br>Mode | ALARM operates on the change between the current input and the last input.                                                                                                                                                                                                        |

| Deadband                    | When enabled, the DB option is incorporated into the HH/H/LL/L limits. These calculated limits are inclusive of the more extreme range, e.g. if the input has been in the high range, the output remains high and does not transition when the input hits the calculated H limit. |

| Operations                  | A flag is set when the input or deviation equals or crosses the corresponding limit. If the DB option is used, the HH, H, LL, L limits are adjusted internally for crossed-limit checking and hysteresis.                                                                         |

**Note:** ALARM automatically tracks the last input, even when you specify normal mode, to facilitate a smooth transition to deviation mode.

# Parameter Block (Middle Node)

The length of the ALARM parameter block is 16 registers:

| Register                    | Content                    |

|-----------------------------|----------------------------|

| Displayed and first implied | Input registers            |

| Second implied              | Output Status, p. 488      |

| Third implied               | Input Status, p. 488       |

| Fourth and fifth implied    | HH limit value             |

| Sixth and seventh implied   | H limit value              |

| Eighth and ninth implied    | L limit value              |

| 10th and 11th implied       | LL limit value             |

| 12th and 13th implied       | Deadband (DB) around limit |

| 14th and 15th implied       | Last input                 |

### **Output Status**

### **Output Status**

| Bit                           | Function                                                            |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------|--|--|--|--|

| 1 4                           | Not used                                                            |  |  |  |  |

| 5                             | 1 = DB set to negative number                                       |  |  |  |  |

| 6                             | 1 = deviation mode chosen with DB option                            |  |  |  |  |

| 7 1 = LL crossed ( $x \le LL$ |                                                                     |  |  |  |  |

| 8                             | 1 = L crossed ( $x \le L$ or $LL < x \le L$ ) with HH/LL option set |  |  |  |  |

| 9                             | 1 = H crossed (x $\geq$ H or H $\leq$ x < HH) with HH/LL option set |  |  |  |  |

| 10                            | 1 = HH crossed ( $x \ge HH$ )                                       |  |  |  |  |

| 11                            | 1 = invalid limits specified                                        |  |  |  |  |

| 12 16                         | Standard output bits (flags) (See Output Flags, p. 476)             |  |  |  |  |

### **Input Status**

### Input Status

| Bit  | Function                                              |

|------|-------------------------------------------------------|

| 1 4  | Standard input bits (flags) (See Input Flags, p. 476) |

| 5    | 1 = deviation mode<br>0 = normal mode                 |

| 6    | 1 = both H/L and HH/LL limits apply                   |

| 7    | 1 = DB enabled                                        |

| 8    | 1 = retain H/L flag when HH/LL limits crossed         |

| 9 16 | Not used                                              |

## **PCFL-AOUT: Analog Output**

99

### At a Glance

### Introduction

This chapter describes the subfunction PCFL-AOUT.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 490  |

| Representation        | 491  |

| Parameter Description | 492  |

### **Short Description**

# Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Signal Processing*, *p. 475*.

The AOUT function is an interface for calculated signals for output modules. It converts the signal to a value in the range 0 ... 4 096.

### Formula

Formula of the AOUT function:

$$OUT = \frac{scale \times (IN - LEU)}{(HEU - LEU)}$$

The meaning of the elements:

| Element | Meaning               |

|---------|-----------------------|

| HEU     | High Engineering Unit |

| IN      | Input                 |

| LEU     | Low Engineering Unit  |

| OUT     | Output                |

| scale   | Scale                 |

## Representation

## Symbol

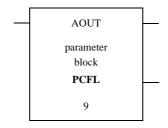

### Representation of the instruction

# Parameter Description

### Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type | Meaning                                                                                                        |

|-------------------------------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None      | ON = enables specified process control function                                                                |

| AOUT (top node)                     |                        |           | Selection of the subfunction AOUT                                                                              |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 9<br>(bottom node)                  |                        | INT, UINT | Length of parameter block for subfunction AOUT (can not be changed)                                            |

| Top output                          | 0x                     | None      | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None      | ON = error                                                                                                     |

## **Parameter Description**

# Parameter Block (Middle Node)

The length of the AOUT parameter block is 9 registers:

| Register                    | Content                    |

|-----------------------------|----------------------------|

| Displayed and first implied | Input in engineering units |

| Second implied              | Output Status, p. 492      |

| Third implied               | Input Status, p. 492       |

| Fourth and fifth implied    | High engineering units     |

| Sixth and seventh implied   | Low engineering units      |

| Eighth and ninth implied    | Output                     |

### **Output Status**

### **Output Status**

| Bit   | Function                                                |

|-------|---------------------------------------------------------|

| 1 7   | Not used                                                |

| 8     | 1 = clamped low                                         |

| 9     | 1 = clamped high                                        |

| 10    | not used                                                |

| 11    | 1 = invalid H/L limits                                  |

| 12 16 | Standard output bits (flags) (See Output Flags, p. 476) |

### **Input Status**

### Input Status

| Bit  | Function                                              |

|------|-------------------------------------------------------|

| 1 4  | Standard input bits (flags) (See Input Flags, p. 476) |

| 5 16 | Not used                                              |

# PCFL-AVER: Average Weighted Inputs Calculate

100

### At a Glance

#### Introduction

This chapter describes the subfunction PCFL-AVER.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 494  |

| Representation        | 495  |

| Parameter Description | 496  |

### **Short Description**

# Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Advanced Calculations*, *p. 475*.

The AVER function calculates the average of up to four weighted inputs.

### Formula

Formula of the AVER function:

$$RES \, = \, \frac{(k + (w_1 \times In_1) + (w_2 \times In_2) + (w_3 \times In_3) + (w_4 \times In_4))}{1 + w_1 + w_2 + w_3 + w_4}$$

The meaning of the elements:

| Element                         | Meaning  |

|---------------------------------|----------|

| In <sub>1</sub> In <sub>4</sub> | Inputs   |

| k                               | Constant |

| RES                             | Result   |

| w <sub>1</sub> w <sub>4</sub>   | Weights  |

### Representation

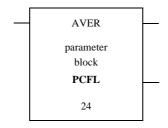

### Symbol

#### Representation of the instruction

# Parameter Description

#### Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type | Meaning                                                                                                        |

|-------------------------------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None      | ON = enables specified process control function                                                                |

| AVER (top node)                     |                        |           | Selection of the subfunction AVER                                                                              |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 24 (bottom node)                    |                        | INT, UINT | Length of parameter block for subfunction AVER (can not be changed)                                            |

| Top output                          | 0x                     | None      | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None      | ON = error                                                                                                     |

### **Parameter Description**

# Parameter Block (Middle Node)

The length of the AVER parameter block is 24 registers:

| Register                    | Content               |

|-----------------------------|-----------------------|

| Displayed and first implied | reserved              |

| Second implied              | Output Status, p. 496 |

| Third implied               | Input Status, p. 497  |

| Fourth and fifth implied    | Value of In1          |

| Sixth and seventh implied   | Value of Inv2         |

| Eighth and ninth implied    | Value of In3          |

| 10th and 11th implied       | Value of In4          |

| 12th and 13th implied       | Value of k            |

| 14th and 15th implied       | Value of wv1          |

| 16th and 17th implied       | Value of wv2          |

| 18th and 19th implied       | Value of wv3          |

| 20th and 21st implied       | Value of wv4          |

| 22nd and 23rd implied       | Value of result       |

#### **Output Status**

#### **Output Status**

| Bit   | Function                                                |

|-------|---------------------------------------------------------|

| 1 9   | Not used                                                |

| 10    | 1 = no inputs activated                                 |

| 11    | 1 = result negative<br>0 = result positive              |

| 12 16 | Standard output bits (flags) (See Output Flags, p. 476) |

#### **Input Status**

#### Input Status

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 | 2 3 | 1 | 3 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|----------------------------------|-----|---|-----|---|---|---|---|---|----|----|----|----|----|----|----|

|----------------------------------|-----|---|-----|---|---|---|---|---|----|----|----|----|----|----|----|

| Bit   | Function                                              |

|-------|-------------------------------------------------------|

| 1 4   | Standard input bits (flags) (See Input Flags, p. 476) |

| 5     | 1 = In4 and w4 are used                               |

| 6     | 1 = In3 and w3 are used                               |

| 7     | 1 = In2 and w2 are used                               |

| 8     | 1 = In1 and w1 are used                               |

| 9     | 1 = k is active                                       |

| 10 16 | Not used                                              |

A weight can be used only when its corresponding input is enabled, e.g. the 20th and 21st implied registers (which contain the value of w4) can be used only when the 10th and 11th implied registers (which contain In4) are enabled. The I in the denominator is used only when the constant is enabled.

# **PCFL-CALC: Calculated preset** formula

101

#### At a Glance

#### Introduction

This chapter describes the subfunction PCFL-CALC.

## What's in this chapter?

This chapter contains the following topics:

| Topic F               |     |  |  |  |  |  |  |

|-----------------------|-----|--|--|--|--|--|--|

| Short Description     | 500 |  |  |  |  |  |  |

| Representation        | 500 |  |  |  |  |  |  |

| Parameter Description | 501 |  |  |  |  |  |  |

#### **Short Description**

# Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Advanced Calculations*, *p. 475*.

The CALC function calculates a preset formula with up to four inputs, each characterized in a separate register of the parameter block.

#### Representation

#### **Symbol**

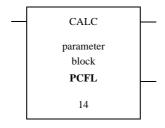

#### Representation of the instruction

### Parameter Description

#### Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type | Meaning                                                                                                        |

|-------------------------------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None      | ON = enables specified process control function                                                                |

| CALC (top node)                     |                        |           | Selection of the subfunction CALC                                                                              |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 14 (bottom node)                    |                        | INT, UINT | Length of parameter block for subfunction CALC (can not be changed)                                            |

| Top output                          | 0x                     | None      | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None      | ON = error                                                                                                     |

### **Parameter Description**

# Parameter Block (Middle Node)

The length of the CALC parameter block is 14 registers:

| Register                    | Content               |

|-----------------------------|-----------------------|

| Displayed and first implied | Reserved              |

| Second implied              | Output Status, p. 501 |

| Third implied               | Input Status, p. 502  |

| Fourth and fifth implied    | Value of input A      |

| Sixth and seventh implied   | Value of input B      |

| Eighth and ninth implied    | Value of input C      |

| 10th and 11th implied       | Value of input D      |

| 12th and 13th implied       | Value of the output   |

#### **Output Status**

#### Output Status

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 1 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|---|

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|---|

| Bit   | Function                                                |

|-------|---------------------------------------------------------|

| 110   | Not used                                                |

| 11    | 1 = bad input code chosen                               |

| 12 16 | Standard output bits (flags) (See Output Flags, p. 476) |

#### **Input Status**

#### Input Status

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Bit   | Function                                              |

|-------|-------------------------------------------------------|

| 1 4   | Standard input bits (flags) (See Input Flags, p. 476) |

| 5 6   | not used                                              |

| 7 10  | Formula Code                                          |

| 11 16 | Not used                                              |

#### Formula Code

| Bit | Bit |   |    | Formula Code                   |

|-----|-----|---|----|--------------------------------|

| 7   | 8   | 9 | 10 |                                |

| 0   | 0   | 0 | 1  | $(A \times B) - (C \times D)$  |

| 0   | 0   | 1 | 1  | $(A \times B)/(C \times D)$    |

| 0   | 1   | 0 | 0  | $A/(B \times C \times D)$      |

| 0   | 1   | 0 | 1  | $(A \times B \times C)/D$      |

| 0   | 1   | 1 | 0  | $A \times B \times C \times D$ |

| 0   | 1   | 1 | 1  | A + B + C + D                  |

| 1   | 0   | 0 | 0  | A×B(C-D)                       |

| 1   | 0   | 0 | 1  | $A[(B/C)^D]$                   |

| 1   | 0   | 1 | 0  | A×LN(B/C)                      |

| 1   | 0   | 1 | 1  | (A-B)-(C-D)/LN[(A-B)/(C-D)]    |

| 1   | 1   | 0 | 0  | $(A/B)^{(-C/D)}$               |

| 1   | 1   | 0 | 1  | (A-B)/(C-D)                    |

### **PCFL-DELAY: Time Delay Queue**

102

#### At a Glance

#### Introduction

This chapter describes the subfunction PCFL-DELAY.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 504  |

| Representation        | 505  |

| Parameter Description | 506  |

#### **Short Description**

### Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Signal Processing*, *p. 475*.

The DELAY function can be used to build a series of readings for time-delay compensation in the logic. Up to 10 sampling instances can be used to delay an input.

All values are carried along in registers, where register x[0] contains the current sampled input. The 10th delay period does not need to be stored. When the 10th instance in the sequence takes place, the value in register x[9] can be moved directly to the output

A DXDONE message is returned when the calculation is complete. The function can be reset by toggling the first-scan bit.

### Representation

### Symbol

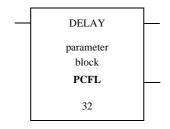

#### Representation of the instruction

# Parameter Description

#### Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type | Meaning                                                                                                        |

|-------------------------------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None      | ON = enables specified process control function                                                                |

| DELAY<br>(top node)                 |                        |           | Selection of the subfunction DELAY                                                                             |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 32 (bottom node)                    |                        | INT, UINT | Length of parameter block for subfunction DELAY (can not be changed)                                           |

| Top output                          | 0x                     | None      | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None      | ON = error                                                                                                     |

### **Parameter Description**

# Parameter Block (Middle Node)

The length of the DELAY parameter block is 32 registers:

| Register                    | Content                     |

|-----------------------------|-----------------------------|

| Displayed and first implied | Input at time n             |

| Second implied              | Output Status, p. 506       |

| Third implied               | Input Status, p. 507        |

| Fourth implied              | Time register               |

| Fifth implied               | Reserved                    |

| Sixth and seventh implied   | Δt (in ms) since last solve |

| Eighth and ninth implied    | Solution interval (in ms)   |

| 10th and 11th implied       | x[0] delay                  |

| 12th and 13th implied       | x[1] delay                  |

| 14th and 15th implied       | x[2] delay                  |

|                             |                             |

| 28th and 29th implied       | x[9] delay                  |

| 30th and 31st implied       | Output registers            |

#### **Output Status**

#### **Output Status**

| Bit  | Function                                                |

|------|---------------------------------------------------------|

| 13   | Not used                                                |

| 4    | 1 = k out of range                                      |

| 5 8  | Count of registers left to be initialized               |

| 9 16 | Standard output bits (flags) (See Output Flags, p. 476) |

#### **Input Status**

#### Input Status

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Bit   | Function                                              |  |  |  |  |

|-------|-------------------------------------------------------|--|--|--|--|

| 1 4   | Standard input bits (flags) (See Input Flags, p. 476) |  |  |  |  |

| 5 8   | Time Delay ≤ 10                                       |  |  |  |  |

| 9 11  | Echo number of registers left to be initialized       |  |  |  |  |

| 12 16 | Not used                                              |  |  |  |  |

# **PCFL-EQN: Formatted Equation Calculator**

103

#### At a Glance

#### Introduction

This chapter describes the subfunction PCFL-EQN.

## What's in this chapter?

This chapter contains the following topics:

| Topic                 | Page |

|-----------------------|------|

| Short Description     | 510  |

| Representation        | 510  |

| Parameter Description | 511  |

#### **Short Description**

# Function Description

**Note:** This instruction is a subfunction of the PCFL instruction. It belongs to the category *Advanced Calculations*, *p. 475*.

The EQN function is a formatted equation calculator. You must define the equation in the parameter block with various codes that specify operators, input selection and inputs.

EQN is used for equations that have four or fewer variables but do not fit into the CALC format. It complements the CALC function by letting you input an equation with floating point and integer inputs as well as operators.

#### Representation

#### **Symbol**

Representation of the instruction

# Parameter Description

Description of the instruction's parameters

| Parameters                          | State RAM<br>Reference | Data Type | Meaning                                                                                                        |

|-------------------------------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| Top input                           | 0x, 1x                 | None      | ON = enables specified process control function                                                                |

| EQN (top node)                      |                        |           | Selection of the subfunction EQN                                                                               |

| parameter<br>block<br>(middle node) | 4x                     | INT, UINT | First in a block of contiguous holding registers where the parameters for the specified subfunction are stored |

| 15 64<br>(bottom node)              |                        | INT, UINT | Length of parameter block for subfunction EQN                                                                  |

| Top output                          | 0x                     | None      | ON = operation successful                                                                                      |

| Bottom output                       | 0x                     | None      | ON = error                                                                                                     |

### **Parameter Description**

# Parameter Block (Middle Node)

The length of the EQN parameter block can be as high as 64 registers:

| Register                    | Content                      |

|-----------------------------|------------------------------|

| Displayed and first implied | Reserved                     |

| Second implied              | Output Status, p. 511        |

| Third implied               | Input Status, p. 512         |

| Fourth and fifth implied    | Variable A                   |

| Sixth and seventh implied   | Variable B                   |

| Eighth and ninth implied    | Variable C                   |

| 10th and 11th implied       | Variable D                   |

| 12th and 13th implied       | Output                       |

| 14th implied                | First Formula Code, p. 512   |

| 15th implied                | Second possible formula code |

|                             |                              |

| 63rd implied                | Last possible formula code   |

#### **Output Status**

#### **Output Status**

|   | _ | _  |   | _ | _ | _ | _   | _ | 4.0 |    | 4.0 | 4.0 |    | 4 - | 4.0 |

|---|---|----|---|---|---|---|-----|---|-----|----|-----|-----|----|-----|-----|

| 1 | ) | :3 | 4 | 5 | h | / | . x | 9 | 1() | 11 | 12  | 1:3 | 14 | 15  | 16  |

|   | _ | _  |   | _ | _ |   | _   | _ |     |    |     |     |    |     |     |

| Bit   | Function                                                |  |  |  |  |

|-------|---------------------------------------------------------|--|--|--|--|

| 1     | Stack error                                             |  |  |  |  |

| 23    | Not used                                                |  |  |  |  |

| 4 8   | Code of last error logged                               |  |  |  |  |

| 9     | 1 = bad operator selection code                         |  |  |  |  |

| 10    | 1 = EQN not fully programmed                            |  |  |  |  |

| 11    | 1 = bad input code chosen                               |  |  |  |  |

| 12 16 | Standard output bits (flags) (See Output Flags, p. 476) |  |  |  |  |

#### **Input Status**

#### Input Status

| ſ |     |   |   |   |   |   |   |   |   |    |     |    |    |    |     |     |

|---|-----|---|---|---|---|---|---|---|---|----|-----|----|----|----|-----|-----|

| ۱ | 4   | 2 | 2 | 4 | _ | 6 | 7 | 0 | _ | 40 | 4.4 | 40 | 40 | 14 | 1 = | 4.0 |

| ۱ | - 1 |   | 3 | 4 | ၁ | ю | / | 0 | 9 | 10 | 11  | 12 | 13 | 14 | 15  | סו  |

| Bit  | Function                                                  |  |  |  |  |

|------|-----------------------------------------------------------|--|--|--|--|

| 1 4  | . 4 Standard input bits (flags) (See Input Flags, p. 476) |  |  |  |  |

| 5    | 1 = Degree/radian option for trigonometry                 |  |  |  |  |

| 6 8  | not used                                                  |  |  |  |  |

| 9 16 | Equation size for display in Concept                      |  |  |  |  |

#### Formula Code

Each formula code in the EQN function defines either an input selection code or an operator selection code.

Formula Code (Parameter Block)

| Bit   | Function                         |

|-------|----------------------------------|

| 1 4   | Not used                         |

| 5 8   | Definition of input selection    |

| 9 11  | Not used                         |

| 12 16 | Definition of operator selection |

840 USE 506 00 October 2002

512

#### **Input Selection**

| Bit |   |   |   | Input Selection        |

|-----|---|---|---|------------------------|

| 5   | 6 | 7 | 8 |                        |

| 0   | 0 | 0 | 0 | Use operator selection |

| 0   | 0 | 0 | 1 | Float input            |

| 0   | 0 | 1 | 1 | 16-bit integer         |

| 1   | 0 | 0 | 0 | Variable A             |

| 1   | 0 | 0 | 1 | Variable B             |

| 1   | 0 | 1 | 0 | Variable C             |

| 1   | 0 | 1 | 1 | Variable D             |

#### **Operator Selection**

| Bit | Bit |    |    |    | Operator Selection     |

|-----|-----|----|----|----|------------------------|

| 12  | 13  | 14 | 15 | 16 |                        |

| 0   | 0   | 0  | 0  | 0  | No operation           |

| 0   | 0   | 0  | 0  | 1  | Absolute value         |

| 0   | 0   | 0  | 1  | 0  | Addition               |

| 0   | 0   | 0  | 1  | 1  | Division               |

| 0   | 0   | 1  | 0  | 0  | Exponent               |

| 0   | 0   | 1  | 1  | 1  | LN (natural logarithm) |

| 0   | 1   | 0  | 0  | 0  | G (logarithm)          |

| 0   | 1   | 0  | 0  | 1  | Multiplication         |

| 0   | 1   | 0  | 1  | 0  | Negation               |

| 0   | 1   | 0  | 1  | 1  | Power                  |

| 0   | 1   | 1  | 0  | 0  | Square root            |

| 0   | 1   | 1  | 0  | 1  | Subtraction            |

| 0   | 1   | 1  | 1  | 0  | Sine                   |

| 0   | 1   | 1  | 1  | 1  | Cosine                 |

| 1   | 0   | 0  | 0  | 0  | Tangent                |

| 1   | 0   | 0  | 0  | 1  | Arcsine                |

| 1   | 0   | 0  | 1  | 0  | Arccosine              |

| 1   | 0   | 0  | 1  | 1  | Arctangent             |

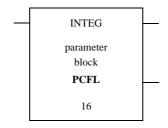

# PCFL-INTEG: Integrate Input at Specified Interval

104

#### At a Glance

#### Introduction

This chapter describes the subfunction PCFL-INTEG.

## What's in this chapter?

This chapter contains the following topics:

| Торіс                 | Page |

|-----------------------|------|