Concept Block Library LL984 Volume 1 840 USE 506 00 eng Version 2.6

© 2002 Schneider Electric All Rights Reserved

## **Table of Contents**

|           | About the book                                                                                                                                                                                                                                                                                                                                                                           | XI                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Part I    | General Information                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |

| Chapter 1 | Instructions                                                                                                                                                                                                                                                                                                                                                                             |                                                                                       |

| Chapter 2 | Instruction Groups         At a Glance         Instruction Groups         ASCII Functions         Counters and Timers Instructions         Fast I/O Instructions         Loadable DX         Math Instructions         Matrix Instructions         Miscellaneous         Move Instructions         Skips/Specials         Special Instructions         Coils, Contacts and Interconnects | . 5<br>. 6<br>. 7<br>. 7<br>. 8<br>. 9<br>. 9<br>. 11<br>. 12<br>. 13<br>. 13<br>. 14 |

| Chapter 3 | Closed Loop Control / Analog Values                                                                                                                                                                                                                                                                                                                                                      | 15<br>16<br>17<br>21                                                                  |

| Chapter 4 | Formatting Messages for ASCII READ/WRIT Operations         At a Glance       Formatting Messages for ASCII READ/WRIT Operations         Format Specifiers       Special Set-up Considerations for Control/Monitor Signals Format                                                                                                                                                         | 29<br>30<br>31                                                                        |

| Chapter 5  | Interrupt Handling                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------|

| Chapter 6  | Subroutine Handling         39           Subroutine Handling         39                                                  |

| Chapter 7  | Installation of DX Loadables                                                                                             |

| Chapter 8  | Coils, Contacts and Interconnects43At a Glance43Coils44Contacts46Interconnects (Shorts)48                                |

| Part II    | Instruction Descriptions                                                                                                 |

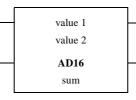

| Chapter 9  | AD16: Ad 16 Bit       55         At a Glance       55         Short Description       56         Representation       56 |

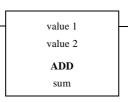

| Chapter 10 | ADD: Addition                                                                                                            |

| Chapter 11 | AND: Logical And 59                                                                                                      |

| Chapter 12 | BCD: Binary to Binary Code 63                                                                                            |

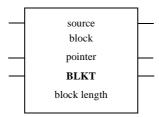

| Chapter 13 | BLKM: Block Move65                                                                                                       |

| Chapter 14 | BLKT: Block to Table                                                                                                     |

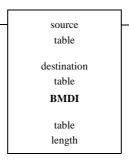

| Chapter 15 | BMDI: Block Move with Interrupts Disabled73                                                                              |

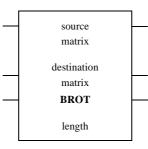

| Chapter 16 | BROT: Bit Rotate                                                                                                         |

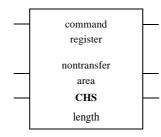

| Chapter 17 | CHS: Configure Hot Standby 79                                                                                            |

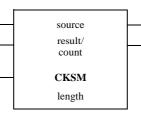

| Chapter 18 | CKSM: Check Sum                                                                                                          |

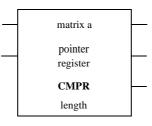

| Chapter 19 | CMPR: Compare Register 89                                                                                                |

| Chapter 20 | COMP: Complement a Matrix                                                                                                |

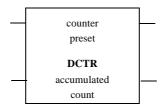

| Chapter 21 | DCTR: Down Counter                                                                                                       |

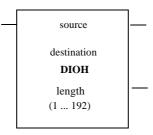

| Chapter 22 | DIOH: Distributed I/O Health                                                                                             |

| Chapter 23 | DIV: Divide                                                                                                              |

| Chapter 24 | DLOG: Data Logging for PCMCIA Read/Write Support107                   |

|------------|-----------------------------------------------------------------------|

| Chapter 25 | DRUM: DRUM Sequencer113                                               |

| Chapter 26 | DV16: Divide 16 Bit117                                                |

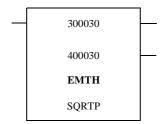

| Chapter 27 | EMTH: Extended Math121                                                |

| Chapter 28 | EMTH-ADDDP: Double Precision Addition127                              |

| Chapter 29 | EMTH-ADDFP: Floating Point Addition131                                |

| Chapter 30 | EMTH-ADDIF: Integer + Floating Point Addition135                      |

| Chapter 31 | EMTH-ANLOG: Base 10 Antilogarithm                                     |

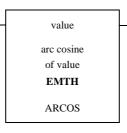

| Chapter 32 | EMTH-ARCOS: Floating Point Arc Cosine of an Angle<br>(in Radians)143  |

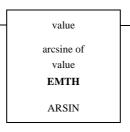

| Chapter 33 | EMTH-ARSIN: Floating Point Arcsine of an Angle<br>(in Radians)147     |

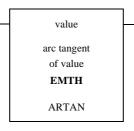

| Chapter 34 | EMTH-ARTAN: Floating Point Arc Tangent of an Angle<br>(in Radians)151 |

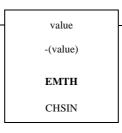

| Chapter 35 | EMTH-CHSIN: Changing the Sign of a<br>Floating Point Number155        |

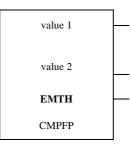

| Chapter 36 | EMTH-CMPFP: Floating Point Comparison159                              |

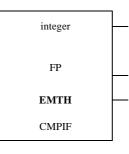

| Chapter 37 | EMTH-CMPIF: Integer-Floating Point Comparison163                      |

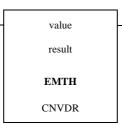

| Chapter 38 | EMTH-CNVDR: Floating Point Conversion of Degrees to Radians           |

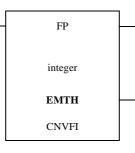

| Chapter 39 | EMTH-CNVFI: Floating Point to Integer Conversion171                   |

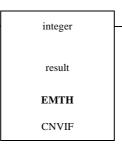

| Chapter 40 | EMTH-CNVIF: Integer-to-Floating Point Conversion175                   |

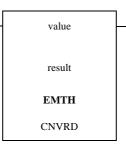

| Chapter 41 | EMTH-CNVRD: Floating Point Conversion of Radians to Degrees           |

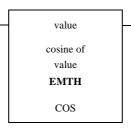

| Chapter 42 | EMTH-COS: Floating Point Cosine of an Angle<br>(in Radians)           |

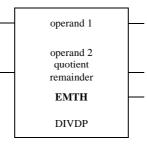

| Chapter 43 | EMTH-DIVDP: Double Precision Division187                              |

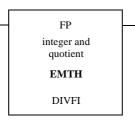

| Chapter 44 | EMTH-DIVFI: Floating Point Divided by Integer191                      |

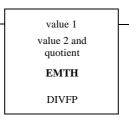

| Chapter 45 | EMTH-DIVFP: Floating Point Division195                                |

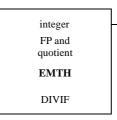

| Chapter 46 | EMTH-DIVIF: Integer Divided by Floating Point                 |

|------------|---------------------------------------------------------------|

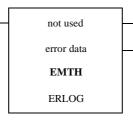

| Chapter 47 | EMTH-ERLOG: Floating Point Error Report Log                   |

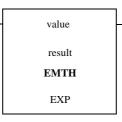

| Chapter 48 | EMTH-EXP: Floating Point Exponential Function                 |

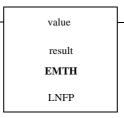

| Chapter 49 | EMTH-LNFP: Floating Point Natural Logarithm                   |

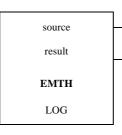

| Chapter 50 | EMTH-LOG: Base 10 Logarithm 215                               |

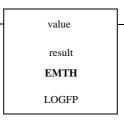

| Chapter 51 | EMTH-LOGFP: Floating Point Common Logarithm 219               |

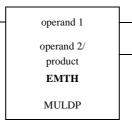

| Chapter 52 | EMTH-MULDP: Double Precision Multiplication                   |

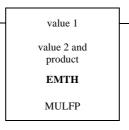

| Chapter 53 | EMTH-MULFP: Floating Point Multiplication                     |

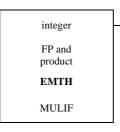

| Chapter 54 | EMTH-MULIF: Integer x Floating Point Multiplication 231       |

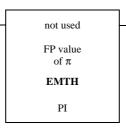

| Chapter 55 | EMTH-PI: Load the Floating Point Value of "Pi"                |

| Chapter 56 | EMTH-POW: Raising a Floating Point Number to an Integer Power |

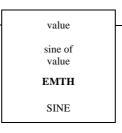

| Chapter 57 | EMTH-SINE: Floating Point Sine of an Angle (in Radians) . 243 |

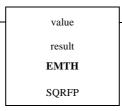

| Chapter 58 | EMTH-SQRFP: Floating Point Square Root                        |

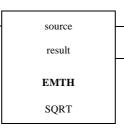

| Chapter 59 | EMTH-SQRT: Floating Point Square Root                         |

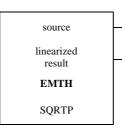

| Chapter 60 | EMTH-SQRTP: Process Square Root                               |

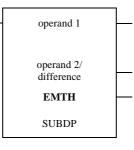

| Chapter 61 | EMTH-SUBDP: Double Precision Subtraction                      |

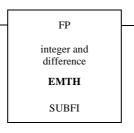

| Chapter 62 | EMTH-SUBFI: Floating Point - Integer Subtraction              |

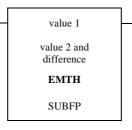

| Chapter 63 | EMTH-SUBFP: Floating Point Subtraction                        |

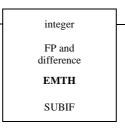

| Chapter 64 | EMTH-SUBIF: Integer - Floating Point Subtraction 271          |

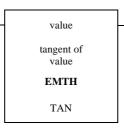

| Chapter 65 | EMTH-TAN: Floating Point Tangent of an Angle<br>(in Radians)  |

| Index      | The chapters marked gray are not included in this volume.     |

| Chapter 66 | ESI: Support of the ESI Module                                |

| Chapter 67 | EUCA: Engineering Unit Conversion and Alarms                  |

|            |                                                               |

| Chapter 68 | FIN: First In                           |

|------------|-----------------------------------------|

| Chapter 69 | FOUT: First Out                         |

| Chapter 70 | FTOI: Floating Point to Integer         |

| Chapter 71 | HLTH: History and Status Matrices       |

| Chapter 72 | IBKR: Indirect Block Read               |

| Chapter 73 | IBKW: Indirect Block Write              |

| Chapter 74 | ICMP: Input Compare                     |

| Chapter 75 | ID: Interrupt Disable                   |

| Chapter 76 | IE: Interrupt Enable                    |

| Chapter 77 | IMIO: Immediate I/O                     |

| Chapter 78 | IMOD: Interrupt Module Instruction357   |

| Chapter 79 | ITMR: Interrupt Timer                   |

| Chapter 80 | ITOF: Integer to Floating Point         |

| Chapter 81 | JSR: Jump to Subroutine                 |

| Chapter 82 | LAB: Label for a Subroutine             |

| Chapter 83 | LOAD: Load Flash                        |

| Chapter 84 | MAP 3: MAP Transaction                  |

| Chapter 85 | MBIT: Modify Bit                        |

| Chapter 86 | MBUS: MBUS Transaction                  |

| Chapter 87 | MRTM: Multi-Register Transfer Module405 |

| Chapter 88 | MSTR: Master                            |

| Chapter 89 | MU16: Multiply 16 Bit453                |

| Chapter 90 | MUL: Multiply455                        |

| Chapter 91 | NBIT: Bit Control                       |

| Chapter 92 | NCBT: Normally Closed Bit459            |

| Chapter 93 | NOBT: Normally Open Bit461              |

|            |                                         |

| Chapter 94  | NOL: Network Option Module for Lonworks                        |

|-------------|----------------------------------------------------------------|

| Chapter 95  | OR: Logical OR                                                 |

| Chapter 96  | PCFL: Process Control Function Library                         |

| Chapter 97  | PCFL-AIN: Analog Input                                         |

| Chapter 98  | PCFL-ALARM: Central Alarm Handler                              |

| Chapter 99  | PCFL-AOUT: Analog Output                                       |

| Chapter 100 | PCFL-AVER: Average Weighted Inputs Calculate 493               |

| Chapter 101 | PCFL-CALC: Calculated preset formula                           |

| Chapter 102 | PCFL-DELAY: Time Delay Queue                                   |

| Chapter 103 | PCFL-EQN: Formatted Equation Calculator                        |

| Chapter 104 | PCFL-INTEG: Integrate Input at Specified Interval 515          |

| Chapter 105 | PCFL-KPID: Comprehensive ISA Non Interacting PID 519           |

| Chapter 106 | PCFL-LIMIT: Limiter for the Pv                                 |

| Chapter 107 | PCFL-LIMV: Velocity Limiter for Changes in the Pv 529          |

| Chapter 108 | PCFL-LKUP: Look-up Table                                       |

| Chapter 109 | PCFL-LLAG: First-order Lead/Lag Filter                         |

| Chapter 110 | PCFL-MODE: Put Input in Auto or Manual Mode                    |

| Chapter 111 | PCFL-ONOFF: ON/OFF Values for Deadband                         |

| Chapter 112 | PCFL-PI: ISA Non Interacting PI                                |

| Chapter 113 | PCFL-PID: PID Algorithms                                       |

| Chapter 114 | PCFL-RAMP: Ramp to Set Point at a Constant Rate 561            |

| Chapter 115 | PCFL-RATE: Derivative Rate Calculation over a Specified Timeme |

| Chapter 116 | PCFL-RATIO: Four Station Ratio Controller                      |

| Chapter 117 | PCFL-RMPLN: Logarithmic Ramp to Set Point                      |

| Chapter 118 | PCFL-SEL: Input Selection                                      |

| Chapter 119 | PCFL-TOTAL: Totalizer for Metering Flow                        |

|             |                                                                |

| Chapter 120 | PEER: PEER Transaction591                 |

|-------------|-------------------------------------------|

| Chapter 121 | PID2: Proportional Integral Derivative    |

| Chapter 122 | R —> T: Register to Table609              |

| Chapter 123 | RBIT: Reset Bit613                        |

| Chapter 124 | READ: Read615                             |

| Chapter 125 | RET: Return from a Subroutine621          |

| Chapter 126 | SAVE: Save Flash623                       |

| Chapter 127 | SBIT: Set Bit                             |

| Chapter 128 | SCIF: Sequential Control Interfaces629    |

| Chapter 129 | SENS: Sense                               |

| Chapter 130 | SKPC: Skip (Constants)639                 |

| Chapter 131 | SKPR: Skip (Registers)643                 |

| Chapter 132 | SRCH: Search                              |

| Chapter 133 | STAT: Status                              |

| Chapter 134 | SU16: Subtract 16 Bit                     |

| Chapter 135 | SUB: Subtraction                          |

| Chapter 136 | T>R: Table to Register679                 |

| Chapter 137 | T>T: Table to Table                       |

| Chapter 138 | T.01 Timer: One Hundredth Second Timer687 |

| Chapter 139 | T0.1 Timer: One Tenth Second Timer689     |

| Chapter 140 | T1.0 Timer: One Second Timer691           |

| Chapter 141 | T1MS Timer: One Millisecond Timer693      |

| Chapter 142 | TBLK: Table to Block                      |

| Chapter 143 | TEST: Test of 2 Values703                 |

| Chapter 144 | UCTR: Up Counter705                       |

| Chapter 145 | WRIT: Write                               |

|             |                                           |

| Chapter 146 | XMIT: XMIT Communication Block |

|-------------|--------------------------------|

| Chapter 147 | XMRD: Extended Memory Read     |

| Chapter 148 | XMWT: Extended Memory Write    |

| Chapter 149 | XOR: Exclusive OR              |

| Glossary    |                                |

## About the book

| At a Glance    |                                                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Document Scope | This documentation will help you configure the LL984-instructions from Concept.                                                                    |

| Validity Note  | This documentation is valid for Concept 2.6 under Microsoft Windows 98, Microsoft Windows 2000, Microsoft Windows XP and Microsoft Windows NT 4.x. |

|                | Note: For additional up-to-date notes, please refer to the file README of Concept.                                                                 |

#### Related Document

| Title of Documentation                                       | Reference Number |

|--------------------------------------------------------------|------------------|

| Concept Installation Instruction                             | 840 USE 502 00   |

| Concept User Manual                                          | 840 USE 503 00   |

| Concept IEC Library                                          | 840 USE 504 00   |

| Concept-EFB User Manual                                      | 840 USE 505 00   |

| XMIT Function Block User Guide                               | 840 USE 113 00   |

| Network Option Module for LonWorks                           | 840 USE 109 00   |

| Quantum Hot Standby Planning and Installation Guide          | 840 USE 106 00   |

| Modbus Plus Network Planning and Installation Guide          | 890 USE 100 00   |

| Quantum 140 ESI 062 10 ASCII Interface Module User Guide     | 840 USE 1116 00  |

| Modicon S980 MAP 3.0 Network Interface Controller User Guide | GM-MAP3-001      |

User Comments We welcome your comments about this document. You can reach us by e-mail at TECHCOMM@modicon.com

About the book

## **General Information**

#### Introduction

#### At a Glance

In this part you will find general information about the instruction groups and the use of instructions.

What's in this part?

This part contains the following chapters:

| Chapter | Chaptername                                        | Page |

|---------|----------------------------------------------------|------|

| 1       | Instructions                                       | 3    |

| 2       | Instruction Groups                                 | 5    |

| 3       | Closed Loop Control / Analog Values                | 15   |

| 4       | Formatting Messages for ASCII READ/WRIT Operations | 29   |

| 5       | Interrupt Handling                                 | 37   |

| 6       | Subroutine Handling                                | 39   |

| 7       | Installation of DX Loadables                       | 41   |

| 8       | Coils, Contacts and Interconnects                  | 43   |

**General Information**

## Instructions

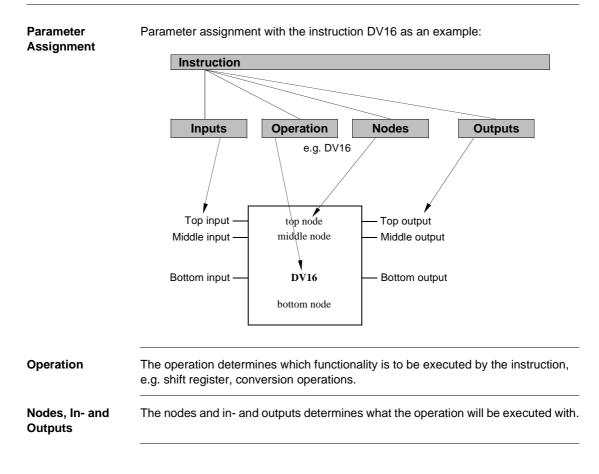

#### **Parameter Assignment of Instuctions**

#### General

Programming for electrical controls involves a user who implements Operational Coded instructions in the form of visual objects organized in a recognizable ladder form. The program objects designed, at the user level, is converted to computer usable OP codes during the download process. the Op codes are decoded in the CPU and acted upon by the controllers firmware functions to implement the desired control.

Each instruction is composed of an operation, nodes required for the operation and in- and outputs.

Instructions

840 USE 506 00 October 2002

# 2

## At a Glance

| Introduction   | In this chapter you will find an overwiew of the instruction groups accompanying instructions. |      |  |  |

|----------------|------------------------------------------------------------------------------------------------|------|--|--|

| What's in this | This chapter contains the following topics:                                                    |      |  |  |

| chapter?       | Торіс                                                                                          | Page |  |  |

|                | Instruction Groups                                                                             | 6    |  |  |

|                | ASCII Functions                                                                                | 7    |  |  |

|                | Counters and Timers Instructions                                                               | 7    |  |  |

|                | Fast I/O Instructions                                                                          | 8    |  |  |

|                | Loadable DX                                                                                    | 9    |  |  |

|                | Math Instructions                                                                              | 9    |  |  |

|                | Matrix Instructions                                                                            | 11   |  |  |

|                | Miscellaneous                                                                                  | 12   |  |  |

|                | Move Instructions                                                                              | 13   |  |  |

|                | Skips/Specials                                                                                 | 13   |  |  |

|                | Special Instructions                                                                           | 14   |  |  |

|                | Coils, Contacts and Interconnects                                                              | 14   |  |  |

#### **Instruction Groups**

General

All instructions are attached to one of the following groups:

- ASCII Functions (See ASCII Functions, p. 7) •

- Counters/Timers (See Counters and Timers Instructions, p. 7) .

- Fast I/O Instructions (See Fast I/O Instructions, p. 8) .

- Loadable DX (See Loadable DX, p. 9) ٠

- Math (See Math Instructions, p. 9) .

- Matrix (See Matrix Instructions, p. 11) .

- Miscellaneous (See Miscellaneous, p. 12) .

- Move (See Move Instructions, p. 13) .

- Skips/Specials (See Skips/Specials, p. 13) •

- Special (See Special Instructions, p. 14) .

- Coils, Contacts and Interconnects, p. 14 .

Overview of all Instructions

Overwiew of instructions per instruction group

DCTR T.01 T0.1 AD16 T1.0 ADD Industruction Selection T1MS BCD UCTR Group Element DIV DV16 Counters/Timers Math Move Matrix Special Skips/Specials Miscellaneous ASCII Eurocions BLKM FTOI BLKT ITOF FIN MU16 FOUT MUL IBKR SU16 SUB TEST IBKW ASCII Functions Fast I/O Instruction Loadable DX R>T SRCH T>R T>T TBLK AND BROT CMPR Close Help on Instruction Help DIOH PCFL COMP PID2 MBIT CHS DRUM STAT NBIT READ NCBT ESI WRIT NOBT JSR EUCA CKSM OR LAB DLOG EMATH RBIT ICMP MAP3 RET BMDI SBIT SKPC LOAD SENS ID MBUS SKPR ΙE MSTR XOR MRTM IMIO SAVE NOL PEER IMOD SCIF XMRD ITMR XMIT MAP3 XMWT

840 USE 506 00 October 2002

#### **ASCII** Functions

#### **ASCII** Functions

This group provides the following instructions:

| Instruction | Meaning              | Available at PLC family |         |          |        |  |

|-------------|----------------------|-------------------------|---------|----------|--------|--|

|             |                      | Quantum                 | Compact | Momentum | Atrium |  |

| READ        | Read ASCII messages  | yes                     | no      | no       | no     |  |

| WRIT        | Write ASCII messages | yes                     | no      | no       | no     |  |

PLCs that support ASCII messaging use instructions called READ and WRIT to handle the sending of messages to display devices and the receiving of messages from input devices. These instructions provide the routines necessary for communication between the ASCII message table in the PLC's system memory and an interface module at the Remote I/O drops. Further information you will find in the chapter *Formatting Messages for ASCII READ/WRIT Operations, p. 29.*

#### **Counters and Timers Instructions**

| Timers<br>Instructions | Instruction | Meaning                                         | Available a                 | at PLC family | y        |        |

|------------------------|-------------|-------------------------------------------------|-----------------------------|---------------|----------|--------|

|                        |             |                                                 | Quantum                     | Compact       | Momentum | Atrium |

|                        | UCTR        | Counts up from 0 to a preset value              | yes                         | yes           | yes      | yes    |

|                        | DCTR        | Counts down from a preset value to 0            | yes                         | yes           | yes      | yes    |

|                        | T1.0        | Timer that increments in seconds                | yes                         | yes           | yes      | yes    |

|                        | T0.1        | Timer that increments in tenths of a second     | yes                         | yes           | yes      | yes    |

|                        | T.01        | Timer that increments in hundredths of a second | yes                         | yes           | yes      | yes    |

|                        | T1MS        | Timer that increments in one millisecond        | yes (CPU<br>242 02<br>only) | yes           | yes      | yes    |

#### Fast I/O Instructions

Fast I/O Instructions The following instructions are designed for a variety of functions known generally as fast I/O updating:

| Instruction | Meaning                             | Available at PLC family |         |          |        |  |

|-------------|-------------------------------------|-------------------------|---------|----------|--------|--|

|             |                                     | Quantum                 | Compact | Momentum | Atrium |  |

| BMDI        | Block move with interrupts disabled | yes                     | yes     | no       | yes    |  |

| ID          | Disable interrupt                   | yes                     | yes     | no       | yes    |  |

| IE          | Enable interrupt                    | yes                     | yes     | no       | yes    |  |

| IMIO        | Immediate I/O instruction           | yes                     | yes     | no       | yes    |  |

| IMOD        | Interrupt module<br>instruction     | yes                     | no      | no       | yes    |  |

| ITMR        | Interval timer interrupt            | no                      | yes     | no       | yes    |  |

Further information you will find in the chapter Interrupt Handling, p. 37.

Note: The Fast I/O Instructions are only available after configuring a CPU without extension.

#### Loadable DX

#### Loadable DX

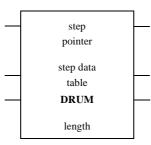

This group provides the following instructions:

| Instruction | Meaning                                     | Available at PLC family |         |          |        |  |

|-------------|---------------------------------------------|-------------------------|---------|----------|--------|--|

|             |                                             | Quantum                 | Compact | Momentum | Atrium |  |

| CHS         | Hot standby (Quantum)                       | yes                     | no      | no       | no     |  |

| DRUM        | DRUM sequenzer                              | yes                     | yes     | no       | yes    |  |

| ESI         | Support of the ESI module<br>140 ESI 062 10 | yes                     | no      | no       | no     |  |

| EUCA        | Engineering unit conversion and alarms      | yes                     | yes     | no       | yes    |  |

| HLTH        | History and status matrices                 | yes                     | yes     | no       | yes    |  |

| ICMP        | Input comparison                            | yes                     | yes     | no       | yes    |  |

| MAP3        | MAP 3 Transaction                           | no                      | no      | no       | no     |  |

| MBUS        | MBUS Transaction                            | no                      | no      | no       | no     |  |

| MRTM        | Multi-register transfer module              | yes                     | yes     | no       | yes    |  |

| NOL         | Transfer to/from the NOL<br>Module          | yes                     | no      | no       | no     |  |

| PEER        | PEER Transaction                            | no                      | no      | no       | no     |  |

| XMIT        | RS 232 Master Mode                          | yes                     | yes     | yes      | no     |  |

Further information you will find in Installation of DX Loadables, p. 41.

#### **Math Instructions**

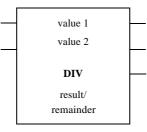

Math<br/>InstructionsTwo groups of instructions that support basic math operations are available. The first<br/>group comprises four integer-based instructions: ADD, SUB, MUL and DIV.The second group contains five comparable instructions, AD16, SU16, TEST, MU16<br/>and DV16, that support signed and unsigned 16-bit math calculations and<br/>comparisons.Three additional instructions, ITOF, FTOI and BCD, are provided to convert the<br/>formats of numerical values (from integer to floating point, floating point to integer,<br/>binary to BCD and BCD to binary). Conversion operations are usful in expanded<br/>math.

#### Integer Based Instructions

#### This part of the group provides the following instructions:

| Instruction | Meaning        | Available at PLC family |         |          |        |  |

|-------------|----------------|-------------------------|---------|----------|--------|--|

|             |                | Quantum                 | Compact | Momentum | Atrium |  |

| ADD         | Addition       | yes                     | yes     | yes      | yes    |  |

| DIV         | Division       | yes                     | yes     | yes      | yes    |  |

| MUL         | Multiplication | yes                     | yes     | yes      | yes    |  |

| SUB         | Subtraction    | yes                     | yes     | yes      | yes    |  |

## Comparable

This part of the group provides the following instructions:

## Instructions

| Instruction | Meaning          | Available at PLC family |         |          |        |  |

|-------------|------------------|-------------------------|---------|----------|--------|--|

|             |                  | Quantum                 | Compact | Momentum | Atrium |  |

| AD16        | Add 16 bit       | yes                     | yes     | yes      | yes    |  |

| DV16        | Divide 16 bit    | yes                     | yes     | yes      | yes    |  |

| MU16        | Multiply 16 bit  | yes                     | yes     | yes      | yes    |  |

| SU16        | Subtract 16 bit  | yes                     | yes     | yes      | yes    |  |

| TEST        | Test of 2 values | yes                     | yes     | yes      | yes    |  |

Format Conversion This part of the group provides the following instructions:

| Instruction | Meaning                                                              | Available at PLC family |         |          |        |  |

|-------------|----------------------------------------------------------------------|-------------------------|---------|----------|--------|--|

|             |                                                                      | Quantum                 | Compact | Momentum | Atrium |  |

| BCD         | Conversion from binary to<br>binary code or binary code<br>to binary | yes                     | yes     | yes      | yes    |  |

| FTOI        | Conversion from floating point to integer                            | yes                     | yes     | yes      | yes    |  |

| ITOF        | Conversion from integer to floating point                            | yes                     | yes     | yes      | yes    |  |

#### **Matrix Instructions**

MatrixA matrix is a sequence of data bits formed by consecutive 16-bit words or registersInstructionsderived from tables. DX matrix functions operate on bit patterns within tables.

Just as with move instructions, the minimum table length is 1 and the maximum table length depends on the type of instruction you use and on the size of the CPU (24bit) in your PLC.

Groups of 16 discretes can also be placed in tables. The reference number used is the first discrete in the group, and the other 15 are implied. The number of the first discrete must be of the first of 16 type 000001, 100001, 000017, 100017, 000033, 100033, ..., etc..

| Instruction | Meaning             | Available a | Available at PLC family |          |        |  |  |

|-------------|---------------------|-------------|-------------------------|----------|--------|--|--|

|             |                     | Quantum     | Compact                 | Momentum | Atrium |  |  |

| AND         | Logical AND         | yes         | yes                     | yes      | yes    |  |  |

| BROT        | Bit rotate          | yes         | yes                     | yes      | yes    |  |  |

| CMPR        | Compare register    | yes         | yes                     | yes      | yes    |  |  |

| COMP        | Complement a matrix | yes         | yes                     | yes      | yes    |  |  |

| MBIT        | Modify bit          | yes         | yes                     | yes      | yes    |  |  |

| NBIT        | Bit control         | yes         | yes                     | no       | yes    |  |  |

| NCBT        | Normally open bit   | yes         | yes                     | no       | yes    |  |  |

| NOBT        | Normally closed bit | yes         | yes                     | no       | yes    |  |  |

| OR          | Logical OR          | yes         | yes                     | yes      | yes    |  |  |

| RBIT        | Reset bit           | yes         | yes                     | no       | yes    |  |  |

| SBIT        | Set bit             | yes         | yes                     | no       | yes    |  |  |

| SENS        | Sense               | yes         | yes                     | yes      | yes    |  |  |

| XOR         | Exclusive OR        | yes         | yes                     | yes      | yes    |  |  |

This group provides the following instructions:

#### **Miscellaneous**

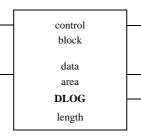

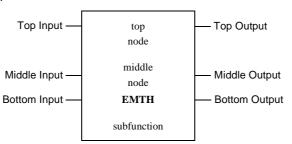

| Miscellaneous | This group provides | s the following instruction |

|---------------|---------------------|-----------------------------|

| mooonanooao   | The group provided  | s and ronowing moa doa      |

| Instruction | Meaning                                       | Available at PLC family                   |         |                                        |        |  |

|-------------|-----------------------------------------------|-------------------------------------------|---------|----------------------------------------|--------|--|

|             |                                               | Quantum                                   | Compact | Momentum                               | Atrium |  |

| CKSM        | Check sum                                     | yes                                       | yes     | yes                                    | yes    |  |

| DLOG        | Data Logging for PCMCIA<br>Read/Write Support | no                                        | yes     | no                                     | no     |  |

| EMTH        | Extended Math Functions                       | yes                                       | yes     | yes                                    | yes    |  |

| LOAD        | Load flash                                    | yes<br>(CPU<br>434 12/<br>534 14<br>only) | yes     | yes<br>(CCC<br>960 x0/<br>980 x0 only) | no     |  |

| MSTR        | Master                                        | yes                                       | yes     | yes                                    | yes    |  |

| SAVE        | Save flash                                    | yes<br>(CPU<br>434 12/<br>534 14<br>only) | yes     | yes<br>(CCC<br>960 x0/<br>980 x0 only) | no     |  |

| SCIF        | Sequential control interfaces                 | yes                                       | yes     | no                                     | yes    |  |

| XMRD        | Extended memory read                          | yes                                       | no      | no                                     | yes    |  |

| XMWT        | Extended memory write                         | yes                                       | no      | no                                     | yes    |  |

#### **Move Instructions**

Move Instructions This group provides the following instructions:

| Instruction | Meaning                | Available at PLC family |         |          |        |  |

|-------------|------------------------|-------------------------|---------|----------|--------|--|

|             |                        | Quantum                 | Compact | Momentum | Atrium |  |

| BLKM        | Block move             | yes                     | yes     | yes      | yes    |  |

| BLKT        | Table to block move    | yes                     | yes     | yes      | yes    |  |

| FIN         | First in               | yes                     | yes     | yes      | yes    |  |

| FOUT        | First out              | yes                     | yes     | yes      | yes    |  |

| IBKR        | Indirect block read    | yes                     | yes     | no       | yes    |  |

| IBKW        | Indirect block write   | yes                     | yes     | no       | yes    |  |

| $R\toT$     | Register to tabel move | yes                     | yes     | yes      | yes    |  |

| SRCH        | Search table           | yes                     | yes     | yes      | yes    |  |

| $T\toR$     | Table to register move | yes                     | yes     | yes      | yes    |  |

| $T\toT$     | Table to table move    | yes                     | yes     | yes      | yes    |  |

| TBLK        | Table to block move    | yes                     | yes     | yes      | yes    |  |

#### Skips/Specials

#### Skips/Specials

This group provides the following instructions:

| Instruction | Meaning                  | Available at PLC family |         |          |        |  |

|-------------|--------------------------|-------------------------|---------|----------|--------|--|

|             |                          | Quantum                 | Compact | Momentum | Atrium |  |

| JSR         | Jump to subroutine       | yes                     | yes     | yes      | yes    |  |

| LAB         | Label for a subroutine   | yes                     | yes     | yes      | yes    |  |

| RET         | Return from a subroutine | yes                     | yes     | yes      | yes    |  |

| SKPC        | Skip (constant)          | yes                     | yes     | yes      | yes    |  |

| SKPR        | Skip (register)          | yes                     | yes     | yes      | yes    |  |

The SKP instruction is a standard instruction in all PLCs. It should be used with caution.

#### DANGER

Inputs and outputs that normally effect control may be unintentionally skipped (or not skipped). SKP is a dangerous instruction that should be used carefully. If inputs

and outputs that normally effect control are unintentionally skipped (or not skipped), the result can create hazardous conditions for personnel and application equipment.

Failure to observe this precaution will result in death or serious injury.

#### **Special Instructions**

SpecialThese instructions are used in special situations to measure statistical events on the<br/>overall logic system or create special loop control situations.

This group provides the following instructions:

| Instruction | Meaning                          | Available at PLC family |         |          |        |

|-------------|----------------------------------|-------------------------|---------|----------|--------|

|             |                                  | Quantum                 | Compact | Momentum | Atrium |

| DIOH        | Distributed I/O health           | yes                     | no      | no       | yes    |

| PCFL        | Process control function library | yes                     | yes     | no       | yes    |

| PID2        | Proportional integral derivative | yes                     | yes     | yes      | yes    |

| STAT        | Status                           | yes                     | yes     | yes      | yes    |

#### **Coils, Contacts and Interconnects**

| Coils, Contacts | <ul> <li>Coils, Contacts and Interconnects are available at all PLC families:</li> <li>Normal coil</li> </ul> |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|--|

| and             |                                                                                                               |  |

|                 |                                                                                                               |  |

| Interconnects   | <ul> <li>Memory-retentive, or latched, coil</li> </ul>                                                        |  |

|                 | <ul> <li>Normally open (N.O.) contact</li> </ul>                                                              |  |

|                 | <ul> <li>Normally closed (N.C.) contact</li> </ul>                                                            |  |

|                 | <ul> <li>Positive transitional (P.T.) contact</li> </ul>                                                      |  |

|                 | <ul> <li>Negative transitional (N.T.) contact</li> </ul>                                                      |  |

|                 | Horizontal Short                                                                                              |  |

|                 |                                                                                                               |  |

Vertical Short

## Closed Loop Control / Analog Values

## At a Glance

| Introduction               | In this chapter you will find general information about configuring closed loop control and using analog values. |      |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------|------|--|

| What's in this<br>chapter? | This chapter contains the following topics:                                                                      |      |  |

|                            | Торіс                                                                                                            | Page |  |

|                            | Closed Loop Control / Analog Values                                                                              | 16   |  |

|                            | PCFL Subfunctions                                                                                                | 17   |  |

|                            | A PID Example                                                                                                    | 21   |  |

|                            | PID2 Level Control Example                                                                                       | 25   |  |

|                            |                                                                                                                  |      |  |

#### **Closed Loop Control / Analog Values**

#### General

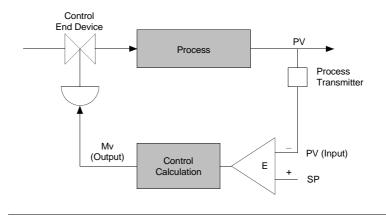

An analog closed loop control system is one in which the deviation from an ideal process condition is measured, analyzed and adjusted in an attempt to obtain and maintain zero error in the process condition. Provided with the Enhanced Instruction Set is a proportional-integral-derivative function block called PID2, which allows you to establish closed loop (or negative feedback) control in ladder logic.

#### Definition of Set Point and Process Variable

The desired (zero error) control point, which you will define in the PID2 block, is called the set point (SP). The conditional measurement taken against SP is called the process variable (PV). The difference between the SP and the PV is the deviation or error (E). E is fed into a control calculation that produces a manipulated variable (Mv) used to adjust the process so that PV = SP (and, therefore, E = 0).

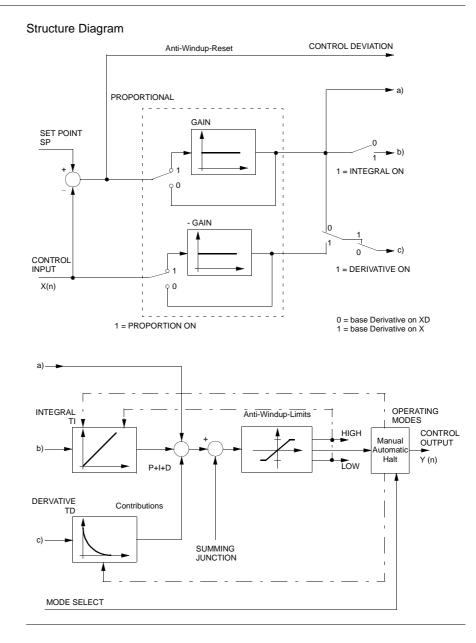

#### General The PCFL instruction gives you access to a library of process control functions utilizing analog values. PCFL operations fall into three major categories: **Advanced Calculations** . Signal Processing . **Regulatory Control** Advanced Advanced calculations are used for general mathematical purposes and are not Calculations limited to process control applications. With advanced calculations, you can create custom signal processing algorithms, derive states of the controlled process, derive statistical measures of the process, etc. Simple math routines have already been offered in the EMTH instruction. The calculation capability included in PCFL is a textual equation calculator for writing custom equations instead of programming a series of math operations one by one. Signal Signal processing functions are used to manipulate process and derived process Processing signals. They can do this in a variety of ways; they linearize, filter, delay and otherwise modify a signal. This category would include functions such as an Analog Input/Output, Limiters, Lead/Lag and Ramp generators. Regulatory Regulatory functions perform closed loop control in a variety of applications. Control Typically, this is a PID (proportional integral derivative) negative feedback control loop. The PID functions in PCFL offer varying degrees of functionality. Function PID has the same general functionality as the PID2 instruction but uses floating point math and represents some options differently. PID is beneficial in cases where PID2 is not suitable because of numerical concerns such as round-off.

#### **PCFL Subfunctions**

Explanation of Formula Elements Meaning of formula elements in the following formulas:

| Formula elements | Meaning                              |

|------------------|--------------------------------------|

| Y                | Manipulated variable output          |

| YP               | Proportional part of the calculation |

| YI               | Integral part of the calculation     |

| YD               | Derivative part of the calculation   |

| Bias             | Constant added to input              |

| ВТ               | Bumpless transfer register           |

| SP               | Set point                            |

| KP               | Proportional gain                    |

| Dt               | Time since last solve                |

| ТІ               | Integral time constant               |

| TD               | Derivative time constant             |

| TD1              | Derivative time lag                  |

| XD               | Error term, deviation                |

| XD_1             | Previous error term                  |

| Х                | Process input                        |

| X_1              | Previous process input               |

#### General Equations

The following general equations are valid:

| Equation                                  | Condition /Requirement       |  |

|-------------------------------------------|------------------------------|--|

| Y = YP + YI + YD + BIAS                   | Integral bit ON              |  |

| Y = YP + YD + BIAS + BT                   | Integral bit OFF             |  |

| $Y_{high} \le Y \le Y_{low}$              | High/low limits              |  |

| with                                      |                              |  |

| YP, YI, YD = f(XD)                        |                              |  |

| $XD = SP - X \pm (GRZ \times (1 - KGRZ))$ | Gain reduction               |  |

| XD = SP - X                               | Gain reduction zone not used |  |

Closed Loop Control / Analog Values

| Proportional | The following equations are valid:                                        |                        |  |

|--------------|---------------------------------------------------------------------------|------------------------|--|

| Calculations | Equation                                                                  | Condition /Requirement |  |

|              | $YP = KP \times XD$                                                       | Proportional bit ON    |  |

|              | $\mathbf{YP} = 0$                                                         |                        |  |

| Integral     | The following equations are valid:                                        |                        |  |

| Calculation  | Equation                                                                  | Condition /Requirement |  |

|              | $YI = YI + KP \times \frac{\Delta t}{TI} \times \frac{XD_{-}1 + XD}{2}$   | Integral bit ON        |  |

|              | YI = 0                                                                    |                        |  |

| Derivative   | The following equations are valid:                                        |                        |  |

| Calculation  | Equation                                                                  | Condition /Requirement |  |

|              | $DXD = X_1 - X$                                                           | Base derivative or PV  |  |

|              | $DXD = XD - X_1$                                                          |                        |  |

|              | $YD = \frac{(TD1 \times YD) + (TD \times KP \times DXD)}{\Delta t + TD1}$ | Derivative bit ON      |  |

|              | $\mathbf{D} = 0$                                                          |                        |  |

Closed Loop Control / Analog Values

Structure Diagram

840 USE 506 00 October 2002

#### **A PID Example**

#### Description

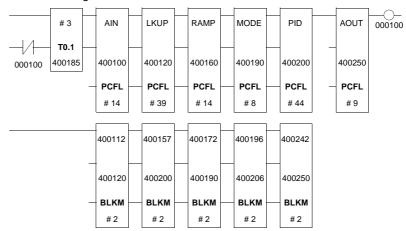

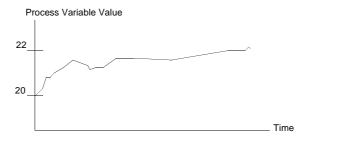

This example illustrates how a typical PID loop could be configured using PCFL function PID. The calculation begins with the AIN function, which takes raw input simulated to cause the output to run between approximately 20 and 22 when the engineering unit scale is set to 0 ... 100.

LL984 Ladder Diagram

The process variable over time should look something like this:

Closed Loop Control / Analog Values

#### Main PID Ladder Logic

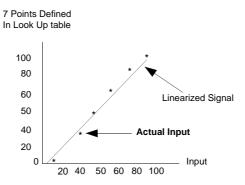

The AIN output is block moved to the LKUP function, which is used to scale the input signal. We do this because the input sensor is not likely to produce highly linear readings; the result is an ideal linear signal:

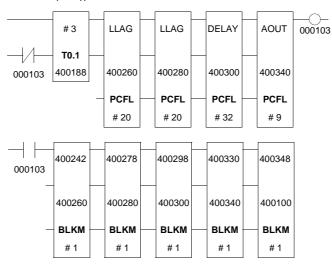

The look-up table output is block moved to the PID function. RAMP is used to control the rise (or fall) of the set point for the PID controller with regard to the rate of ramp and the solution interval. In this example, the set point is established in another logic section to simulate a remote setting. The MODE function is placed after the RAMP so that we can switch between the RAMP-generated set point or a manual value.

Simulated Process

The PID function is actually controlling the process simulated by this logic (value in 400100: 878(Dec)):

The process simulator is comprised of two LLAG functions that act as a filter and input to a DELAY queue that is also a PCFL function block. This arrangement is the equivalent of a second-order process with dead time.

The solution intervals for the LLAG filters do not affect the process dynamics and were chosen to give fast updates. The solution interval for the DELAY queue is set at 1000 ms with a delay of 5 intervals, i.e. 5 s. The LLAG filters each have lead terms of 4 s and lag terms of 10 s. The gain for each is 1.0.

In process control terms the transfer function can be expressed as:

$$Gp(S) = \frac{(4S+1)(4S+1)e^{-5S}}{(10S+1)(10S+1)}$$

The AOUT function is used only to convert the simulated process output control value into a range of 0 ... 4 095, which simulates a field device. This integer signal is used as the process input in the first network.

## **PID Parameters** The PID controller is tuned to control this process at 20.0, using the Ziegler-Nichols tuning method. The resulting controller gain is 2.16, equivalent to a proportional band of 46.3%.

The integral time is set at 12.5 s/repeat (4.8 repeats/ min). The derivative time is initially 3 s, then reduced to 0.3 s to de-emphasize the derivative effect. An AOUT function is used after the PID. It conditions the PID control output by scaling the signal back to an integer for use as the control value.

The entire control loop is preceded by a 0.1 s timer. The target solution interval for the entire loop is 1 s, and the full solve is 1 s. However, the nontime-dependent functions that are used (AIN, LKUP, MODE, and AOUT) do not need to be solved every scan. To reduce the scan time impact, these functions are scheduled to solve less frequently. The example has a loop solve every 3 s, reducing the average scan time dramatically.

**Note:** It is still important to be aware of the maximum scan impact. When programming other loops, you will not want all of the loops to solve on the same scan

#### **PID2 Level Control Example**

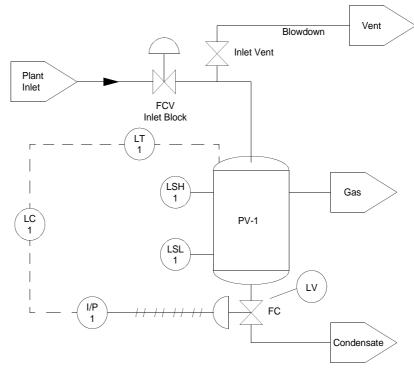

**Description** Here is a simplified P&I diagram for an inlet separator in a gas processing plant. There is a two-phase inlet stream: liquid and gas.

LT-1 4 ... 20 mA level transmitter

I/P-1 4 ... 20 mA current to pneumatic converter

LV-1 control valve, fail CLOSED

LSH-1 high level switch, normally closed

LSL-1 low level switch, normally open

LC-1 level controller

I/P-1 Mv to control the flow into tank T-1

The liquid is dumped from the tank to maintain a constant level. The control objective is to maintain a constant level in the separator. The phases must be separated before processing; separation is the role of the inlet separator, PV-1. If the level controller, LC-1, fails to perform its job, the inlet separator could fill, causing liquids to get into the gas stream; this could severely damage devices such as gas compressors.

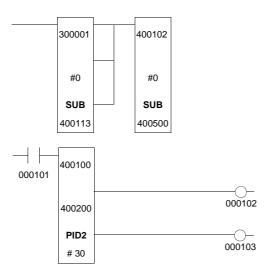

Ladder LogicThe level is controlled by device LC-1, a Quantum controller connected to an analog<br/>input module; I/P-1 is connected to an analog output module. We can implement the<br/>control loop with the following 984 ladder logic:

The first SUB block is used to move the analog input from LT-1 to the PID2 analog input register, 40113. The second SUB block is used to move the PID2 output Mv to the I/O mapped output I/P-1. Coil 00101 is used to change the loop from AUTO to MANUAL mode, if desired. For AUTO mode, it should be ON.

|  | the PID2 b | olock as fol       | lows:                                |                                                                                                  |

|--|------------|--------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|

|  | Register   | Content<br>Numeric | Content<br>Meaning                   | Comments                                                                                         |

|  | 400100     |                    | Scaled PV (mm)                       | PID2 writes this                                                                                 |

|  | 400101     | 2000               | Scaled SP (mm)                       | Set to 2000 mm (half full) initially                                                             |

|  | 400102     | 0000               | Loop output (0 4095                  | PID2 writes this; keep it set to 0 to be safe                                                    |

|  | 400103     | 3500               | Alarm High Set Point (mm)            | If the level rises above 3500 mm, coil 000102 goes ON                                            |

|  | 400104     | 1000               | Alarm Low Set Point (mm)             | If the level drops below 1000 mm, coil 000103 goes ON                                            |

|  | 400105     | 0100               | PB (%)                               | The actual value depends on the process dynamics                                                 |

|  | 400106     | 0500               | Integral constant (5.00 repeats/min) | The actual value depends on the process dynamics                                                 |

|  | 400107     | 0000               | Rate time constant (per min)         | Setting this to 0 turns off the derivative mode                                                  |

|  | 400108     | 0000               | Bias (0 4095)                        | This is set to 0, since we have an integral term                                                 |

|  | 400109     | 4095               | High windup limit (0 4095)           | Normally set to the maximum                                                                      |

|  | 400110     | 0000               | Low windup limit (0 4095)            | Normally set to the minimum                                                                      |

|  | 400111     | 4000               | High engineering range (mm)          | The scaled value of the process<br>variable when the raw input is at<br>4095                     |

|  | 400112     | 0000               | Low engineering range (mm)           | The scaled value of the process variable when the raw input is at 0                              |

|  | 400113     |                    | Raw analog measure<br>(0 4095)       | A copy of the input from the analog<br>input module register (300001)<br>copied by the first SUB |

|  | 400114     | 0000               | Offset to loop counter register      | Zero disables this feature.<br>Normally, this is not used                                        |

|  | 400115     | 0000               | Max loops solved per scan            | See register 400114                                                                              |

**Register Content** Specify the set point in mm for input scaling (E.U.). The full in .....

Closed Loop Control / Analog Values

| Register | Content<br>Numeric | Content<br>Meaning                 | Comments                                                                                                                                                                                                                                                                                            |

|----------|--------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 400116   | 0102               | Pointer to reset feedback          | If you leave this as zero, the PID2<br>function automatically supplies a<br>pointer to the loop output register. If<br>the actual output (400500) could be<br>changed from the value supplied by<br>PID2, then this register should be<br>set to 500 (400500) to calculate the<br>integral properly |

| 400117   | 4095               | Output clamp high (0 4095)         | Normally set to maximum                                                                                                                                                                                                                                                                             |

| 400118   | 0000               | Output clamp low (0 4095)          | Normally set to minimum                                                                                                                                                                                                                                                                             |

| 400119   | 0015               | Rate Gain Limit Constant<br>(2 30) | Normally set to about 15. The actual value depends on how noisy the input signal is. Since we are not using derivative mode, this has no effect on PID2                                                                                                                                             |

| 400120   | 0000               | Pointer to track input             | Used only if the PRELOAD feature<br>is used. If the PRELOAD is not<br>used, this is normally zero                                                                                                                                                                                                   |

The values in the registers in the 400200 destination block are all set by the PID2 block.

## 4

## At a Glance

| Introduction            | In this chapter you will find general information about formatting me<br>READ/WRIT operations. | essages for ASCII |

|-------------------------|------------------------------------------------------------------------------------------------|-------------------|

| What's in this chapter? | This chapter contains the following topics:                                                    | Page              |

|                         | Formatting Messages for ASCII READ/WRIT Operations                                             | 30                |

|                         | Format Specifiers                                                                              | 31                |

|                         | Special Set-up Considerations for Control/Monitor Signals Format                               | 34                |

#### Formatting Messages for ASCII READ/WRIT Operations

#### General

The ASCII messages used in the READ and WRIT instructions can be created via your panel software using the format specifiers described below. Format specifiers are character symbols that indicate:

- The ASCII characters used in the message

- Register content displayed in ASCII character format ٠

- Register content displayed in hexadecimal format ٠

- Register content displayed in integer format .

- Subroutine calls to execute other message formats

## **Overview Format**

The following format specifiers can be used;

Specifiers

| Specifier | Meaning |

|-----------|---------|

|           |         |

| Specifier | Meaning                             |

|-----------|-------------------------------------|

| 1         | ASCII return (CR) and linefeed (LF) |

|           | Enclosure for octal control code    |

|           | Enclosure for ASCII text characters |

| х         | Space indicator                     |

| ()        | Repeat contents of the parentheses  |

| I         | Integer                             |

| L         | Leading zeros                       |

| А         | Alphanumeric                        |

| 0         | Octal                               |

| В         | Binary                              |

| н         | Hexadecimal                         |

## **Format Specifiers**

|              | Field width      | None (defaults to 1)                         |

|--------------|------------------|----------------------------------------------|

|              | Prefix           | None (defaults to 1)                         |

|              | Input format     | Outputs CR, LF; no ASCII characters accepted |

|              |                  |                                              |

| at Specifier | Output format    |                                              |

| at Specifier |                  |                                              |

| at Specifier | Enclosure for or | tal control code                             |

| at Specifier | Enclosure for or | Three digits enclosed in double quotes       |

Format Specifier

#### Enclosure for ASCII text characters

| Field width   | 1 128 characters                                                                            |

|---------------|---------------------------------------------------------------------------------------------|

| Prefix        | None (defaults to 1)                                                                        |

| Input format  | Inputs number of upper and/or lower case printable characters specified by the field width  |

| Output format | Outputs number of upper and/or lower case printable characters specified by the field width |

### Format Specifier

х

**Space indicator**, e.g., 14x indicates 14 spaces left open from the point where the specifier occurs.

| Field width   | None (defaults to 1)               |  |

|---------------|------------------------------------|--|

| Prefix        | 1 99 spaces                        |  |

| Input format  | Inputs specified number of spaces  |  |

| Output format | Outputs specified number of spaces |  |

**Format Specifier**

## fier Repeat contents of the parentheses, e.g., 2 (4x, I5) says repeat 4X, I5 two times

()

| Field width   | None                                                                                |

|---------------|-------------------------------------------------------------------------------------|

| Prefix        | 1 255                                                                               |

| Input format  | Repeat format specifiers in parentheses the number of times specified by the prefix |

| Output format | Repeat format specifiers in parentheses the number of times specified by the prefix |

Format Specifier

Integer, e.g., 15 specifies five integer characters

| Field width   | 1 8 characters                                                                                                                                                                   |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prefix        | 1 99                                                                                                                                                                             |

| Input format  | Accepts ASCII characters 0 9. If the field width is not satisfied, the most significant characters in the field are padded with zeros                                            |

| Output format | Outputs ASCII characters 0 9. If the field width is not satisfied, the most significant characters in the field are padded with zeros. The overflow field consists of asterisks. |

Format Specifier

#### Leading zeros, e.g., L5 specifies five leading zeros

L

| Field width  | 1 8 characters                                                         |

|--------------|------------------------------------------------------------------------|

| Prefix       | 1 99                                                                   |

| Input format | Accepts ASCII characters 0 9. If the field width is not satisfied, the |

## most significant characters in the field are padded with zeros Output format Outputs ASCII characters 0 ... 9. If the field width is not satisfied, the most significant characters in the field are padded with zeros. The overflow field consists of asterisks.

#### **Format Specifier**

Alphanumeric, e.g., A27 specifies 27 alphanumeric characters, no suffix allowed

| Field width   | None (defaults to 1)                                                                    |

|---------------|-----------------------------------------------------------------------------------------|

| Prefix        | 1 99                                                                                    |

| Input format  | Accepts any 8-bit character except reserved delimiters such as CR, LF, ESC, BKSPC, DEL. |

| Output format | Outputs any 8-bit character                                                             |

А

## 0

Format Specifier Octal, e.g., 02 specifies two octal characters

| Field width   | 1 6 characters                                                                                                                                    |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Prefix        | 1 99                                                                                                                                              |

| Input format  | Accepts ASCII characters 0 7. If the field width is not satisfied, the most significant characters are padded with zeros.                         |

| Output format | Outputs ASCII characters 0 7. If the field width is not satisfied, the most significant characters are padded with zeros. No overflow indicators. |

Format Specifier

в

н

Binary, e.g., B4 specifies four binary characters

| Field width   | 1 16 characters                                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prefix        | 1 99                                                                                                                                                  |

| Input format  | Accepts ASCII characters 0 and 1. If the field width is not satisfied, the most significant characters are padded with zeros.                         |

| Output format | Outputs ASCII characters 0 and 1. If the field width is not satisfied, the most significant characters are padded with zeros. No overflow indicators. |

**Format Specifier**

#### Hexadecimal, e.g., H2 specifies two hex characters

|               | •                                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field width   | 1 4 characters                                                                                                                                            |

| Prefix        | 1 99                                                                                                                                                      |

| Input format  | Accepts ASCII characters 0 9 and A F. If the field width is not satisfied, the most significant characters are padded with zeros.                         |

| Output format | Outputs ASCII characters 0 9 and A F. If the field width is not satisfied, the most significant characters are padded with zeros. No overflow indicators. |

#### Special Set-up Considerations for Control/Monitor Signals Format

0 = do not control RTS

**General** To control and monitor the signals used in the messaging communication, specify code 1002 in the first register of the control block (the register displayed in the top node). Via this format, you can control the RTS and CTS lines on the port used for messaging.

**Note:** In this format, only the local port can be used for messaging, i.e., a parent PLC cannot monitor or control the signals on a child port. Therefore, the port number specified in the fifth implied node of the control block must always be 1.

The first three registers in the data block (the displayed register and the first and second implied registers in the middle node) have predetermined content:

| Register       | Content                      |

|----------------|------------------------------|

| Displayed      | Stores the control mask word |

| First implied  | Stores the control data word |

| Second implied | Stores the status word       |

These three data block registers are required for this format, and therefore the allowable range for the length value (specified in the bottom node) is 3 ... 255.

| Jsag  | je of                                  | wor | d:    |       |                  |  |  |  |  |  |  |

|-------|----------------------------------------|-----|-------|-------|------------------|--|--|--|--|--|--|

| 1     | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |     |       |       |                  |  |  |  |  |  |  |

| Bit   |                                        | F   | unct  | ion   |                  |  |  |  |  |  |  |

| 1     |                                        |     | •     |       | n be i<br>nnot l |  |  |  |  |  |  |

| 2 - 1 | 5                                      | N   | ot us | ed    |                  |  |  |  |  |  |  |

| 16    |                                        | 1   | = co  | ntrol | RTS              |  |  |  |  |  |  |

Control Mask Word

| Control | Data |

|---------|------|

| Word    |      |

| lsag<br>1           | ge of<br>2 | wor<br>3 | d:<br>4         | 5     | 6     | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------|------------|----------|-----------------|-------|-------|----|---|---|----|----|----|----|----|----|----|

|                     |            |          |                 |       |       |    |   |   |    |    |    |    |    |    |    |

| Bit Function        |            |          |                 |       |       |    |   |   |    |    |    |    |    |    |    |

| 1                   |            | 1        | 1 = take port   |       |       |    |   |   |    |    |    |    |    |    |    |

|                     |            | 0        | 0 = return port |       |       |    |   |   |    |    |    |    |    |    |    |

| 2 - 1               | 5          | N        | Not used        |       |       |    |   |   |    |    |    |    |    |    |    |

| 16 1 = activate RTS |            |          |                 |       |       |    |   |   |    |    |    |    |    |    |    |

|                     |            | 0        | = de            | activ | ate R | TS |   |   |    |    |    |    |    |    |    |

#### Status Word

#### Usage of word: 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Bit Function 1 1 = port taken 2 1 = port ACTIVE as Modbus slave 3 - 13 Not used 14 1 = DSR ON 15 1 = CTS ON 16 1 = RTS ON

## Interrupt Handling

## 5

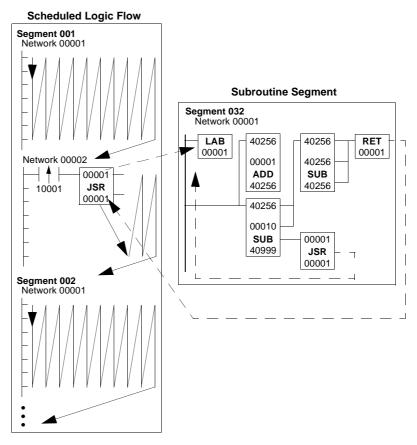

## Interrupt Handling

| Interrupt-related<br>Performance | The interrupt-related instructions operate with minimum processing overhead. The performance of interrupt-related instructions is especially critical. Using a interval timer interrupt (ITMR) instruction adds about 6% to the scan time of the scheduled ladder logic, this increase does not include the time required to execute the interrupt handler subroutine associated with the interrupt. |                                                                                                                                                            |                                                                                          |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|